IDC20A Debug Probe

ほぼすべての組込みプラットフォームの業界標準

IDC20Aデバッグプローブは、もともとArm® CoreSight™デバッグインフラを備えたSoCをデバッグするために設計されました。Arm アーキテクチャの大成功により、このデバッグコンセプトは、組み込み市場におけるマルチコアシステムのデファクトデバッグ標準となりました。

今日、IDC20Aデバッグプローブは、CoreSight™の有無にかかわらず、SoCをデバッグするための さまざまなアーキテクチャとプロトコルをサポートしており、ローターバッハは最も成功しているデバッグプローブです。

あらゆるプロジェクトに対応する高速で信頼性の高いデバッグプローブ

IDC20Aデバッグプローブは、最大限の柔軟性を持つように設計されています。広い入力電圧範囲と優れたシグナルインテグリティを備えた、組み込み市場全体で最も一般的なピン配置を 特長とし、一般的な産業用アプリケーションから高速モバイルデバイス設計まで、多くのターゲットに最適です。

ヘテロジニアスチップにも対応

When debugging multicore systems, it becomes essential that the debug probe is able to concurrently control cores of various architectures within one SoC. The IDC20A Debug Probe provides this flexibility and supports a wide range of architectures.

あらゆるターゲットに完璧にフィット

IDC20Aデバッグプローブは、組み込み市場で最も一般的なピンアウトを提供します。豊富なアダプターの選択肢とともに、幅広いターゲットに最適です。

高速転送とシグナルインテグリティ

With transceivers located close to the target, the IDC20A Debug Probe provides highest signal integrity at highest transfer speeds. For appropriate processors the high throughput performance even allows some real time tracing.

0.4Vからの広い電圧範囲

0.4Vまでの 低I/O電圧を持つ高速ターゲットや、5VまでのI/O電圧を持つ標準的な産業用アプリケーションをサポートします。

あらゆるチップをコントロール

IDC20Aは、移動体通信、医療、民生用電子機器、半導体、航空宇宙、産業など、多くの業界で標準的に使用されているデバッグプローブです。現在確立されているマイクロアーキテクチャから、流行の新しいアーキテクチャまで、数十種類のアーキテクチャをサポートしています。IDC20Aは、超小型マイクロコントローラから最も複雑なSoC、ソフトコア(FPGAに実装)、DSPなどのさまざまなサブコントローラまでのチップをカバーしています。

Arm/Cortex

AndesCore

APEX

APS3

ARC

AVR8

ARP32

Beyond

C166SV2

C2000

C5000

C6000

C7000

CEVA-X

HC11

Hexagon

i8051

M32R

Meta

Mico32

MicroBlaze

NIOS-II

PRU

RISC-V

SDMA

SH

SRP

StarCore

STM8

STRED

Synopsys-ASIP

Teak/TeakLite

Ubicom32

Xtensa

ZSP

78k

ユニバーサルデバッグプロトコルのサポート

JTAG

JTAGは、ほとんどのCPUで一般的に利用できるデバッグプロトコルです。バウンダリースキャンデバイステストから派生したJTAGは、外部ツールがチップ内部のテストアクセスポイント(TAP)コントローラと通信することを可能にします。TAPはチップ内のデバッグインフラへのアクセスポイントです。TAPは、1つのデバッグプローブを介して複数のコアのデバッグを可能にするためにチェーン接続することができます。

cJTAG(コンパクトJTAG)(IEEE 1149.7)

コンパクトJTAG(cJTAG)は、デバッガとコアのテストアクセスポイント(TAP)間のJTAG通信をシリアル化することで、デバッグインターフェイスのピン数を削減するJTAGベースの技術です。複数のチップをスター型トポロジーでサポートできます。通常のJTAGと比較して、デバッグ性能は若干低下しますが、物理ピンのコストを削減できます。

SWD/SWO

SWD(Serial Wire Debug)は、Arm®によって定義された2ピンのデバッグインターフェイスで、CoreSight™デバッグインフラストラクチャに最高のパフォーマンスでアクセスできるように最適化されています。シリアルワイヤ出力(SWO)は、SWDのオプションの拡張ピンです。プロセッサにSWOピンがある場合、IDC20Aデバッグプローブは、コードインスツルメンテーションとデータアクセス*の両方からトレースデータを受信できます。

*PowerDebug E40/PowerDebug Pro およびそれ以降のベースモジュールに対応。

Renesas Single-Wire UART

RL78プロセッサは、RESETピンとTOOL0ピンを使用するUARTのような1ライン デバッグインターフェースを介してデバッグされますが、旧型の78K0Rプロセッサは追加の信号TOOL1を使用します。

UPDI

Microchip が設計した Unified Program and Debug Interface (UPDI) は、チップのリセットピンでもある 1 つのピンを通して tinyAVR® と megaAVR® デバイスをデバッグおよびプログラムするための独自のプロトコルです。これらのデバイスはシリアル ペリフェラル インターフェース (SPI) 経由でもプログラムできます。

Andes Serial Debug Port

シリアルデバッグポートは、アンデステクノロジー社が設計したAndesCore™およびRISC-Vプロセッサ用の2線式オプションです。

お客様のアーキテクチャに合ったIDC20Aプローブを入手する

IDC20A Debug Probe with debug license to debug Cortex-M cores (Armv6/7/8-M) and SecurCore SC000/SC300, via JTAG, cJTAG (IEEE 1149.7), or Serial Wire Debug (SWD). Includes licenses to debug and trace Cortex-M cores and SecurCore SC000/SC300, as well as debug GTM and IPU cores. Includes TRACE32 software for Windows, Linux and macOS on DVD or via download. With legacy debug modules LA-7702/LA-7704 only JTAG is supported. Voltage range 0.4V to 5.0V.

IDC20A debug cable for 64-bit RISC-V cores (RV64) usable with a PowerDebug base module supporting JTAG, cJTAG and Serial Wire Debug Port (0.4 - 5.0V). Includes license for multicore debugging. Includes TRACE32 software for Windows, Linux and macOS on DVD or via download. Requires TRACE32 software R.2020.09 or newer. Requires a PowerDebug base module. A range of converters are available to adapt to different target connectors (including MIPI pinouts).

supports Xtensa Cores from Tensilica via an ARM JTAG interface core trace decoding for TRAX (Trace RAM within core logic) included includes software for Windows, Linux and MacOSX requires Power Debug Module IDC20A debug cable requires LA-3763 if 14 pin JTAG (Xtensa) connector is used

Supports Xtensa Cores from Tensilica via an ARM JTAG interface Core trace decoding for TRAX (Trace RAM within core logic) included IDC20A debug cable, which supports 5-pin standard JTAG, cJTAG (IEEE 1149.7) and serial Wire Debug (SWD), (0.4V - 5V) Includes software for Windows, Linux and macOS Requires PowerDebug module Requires LA-3763 if 14 pin JTAG (Xtensa) connector is used

IDC20A debug cable for 32-bit ARC cores from Synopsys inlcuding ARC EM, ARC HS3x/4x, ARC EV/VPX/NPX, ARC 600/700, ARCtangent-A4/A5 usable with a PowerDebug base module supporting JTAG, cJTAG and Serial Wire Debug Port (0.4 - 5.0V). Includes TRACE32 software for Windows, Linux and macOS on DVD or via download. Requires a PowerDebug base module. For ARC-V you require a RISC-V probe instead (LA-3200 or LA-3201).

IDC20A debug cable for Hexagon DSPs and NPUs from Qualcomm usable with a PowerDebug base module supporting JTAG, cJTAG (IEEE 1149.7) and Serial Wire Debug Port (SWD). Voltage range 0.4V to 5.0V. Includes license for multicore debugging and trace decoding. Includes TRACE32 software for Windows, Linux and macOS on DVD or via download. Requires a PowerDebug base module.

IDC20A Debug Probe with a license for debugging of C28x and C29x microcontrollers via JTAG, cJTAG (IEEE 1149.7), or Serial Wire Debug (SWD). Includes licenses to debug Control Law Accelerator (CLA). Includes licenses for onchip trace "PC Trace". ("PC Trace" supports up to 128 program branches.) Includes TRACE32 software for Windows, Linux and macOS on DVD or via download. Requires a PowerDebug base module. Requires LA-3780 if you need to adapt to a TI-14 or TI-20-Compact target header. Voltage range 0.4V to 5.0V.

Supports C6xxx. Uses IDC20A debug cable, which supports 5-pin standard JTAG, cJTAG (IEEE 1149.7) and Serial Wire Debug (SWD), (0.4V - 5V) Includes software for Windows, Linux and macOS. Requires PowerDebug base module. Requires LA-7748 if 14 pin TI target adapter is used.

Supports C7000. Uses IDC20A debug cable, which supports 5-pin standard JTAG, cJTAG (IEEE 1149.7) and Serial Wire Debug (SWD), (0.4V - 5V) Includes software for Windows, Linux and macOS. Requires PowerDebug base module. Requires LA-7748 if 14 pin TI target adapter is used.

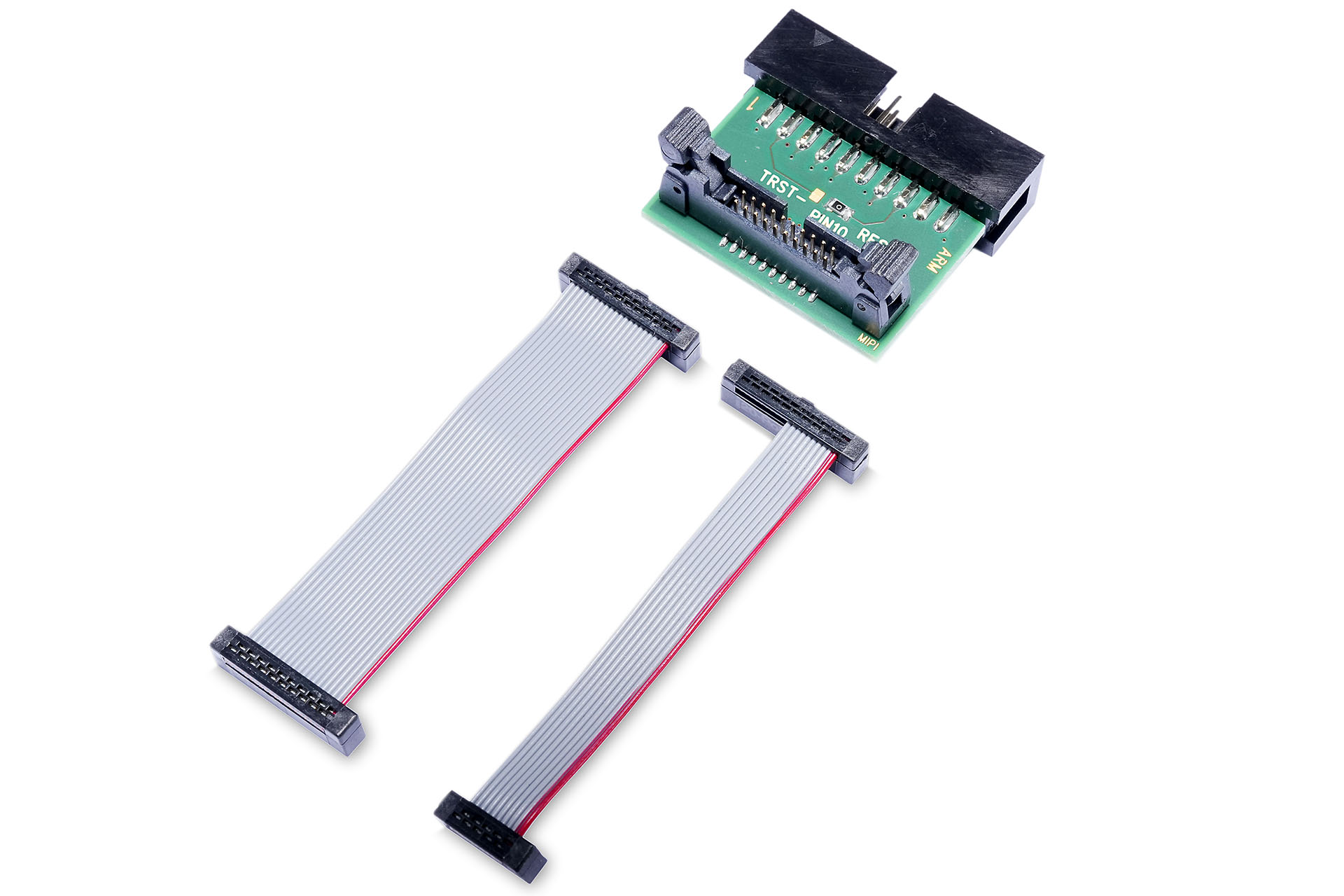

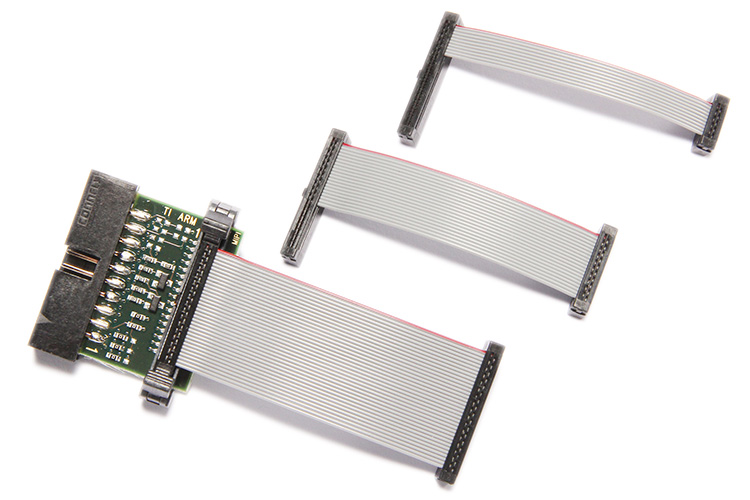

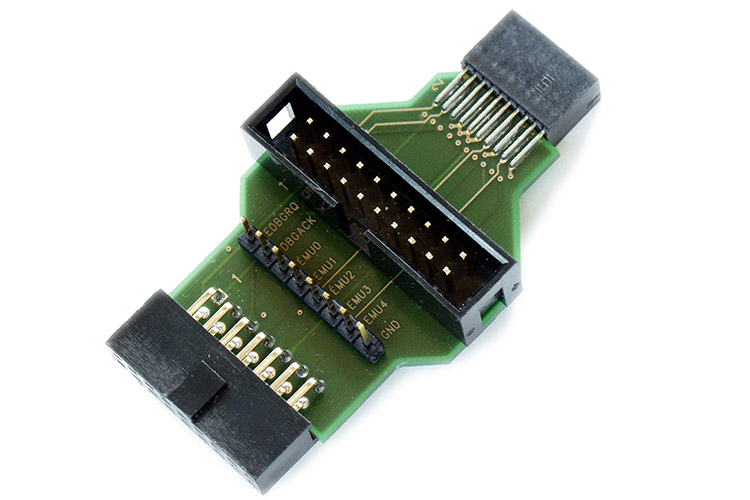

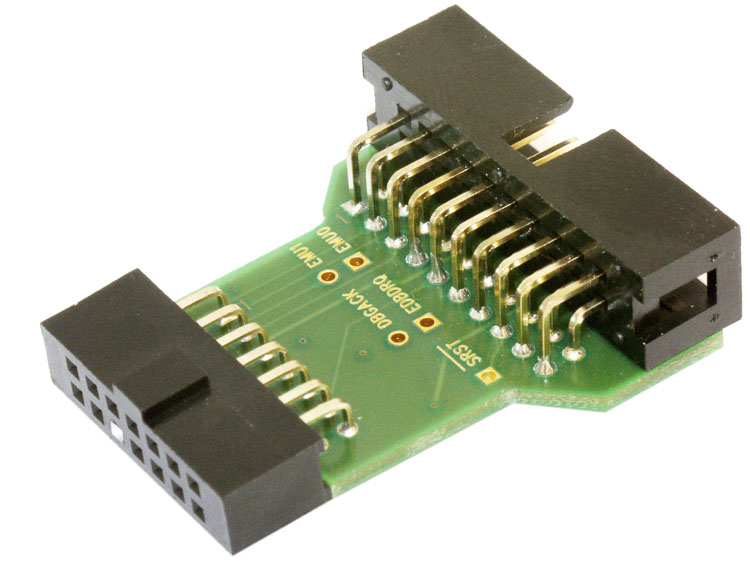

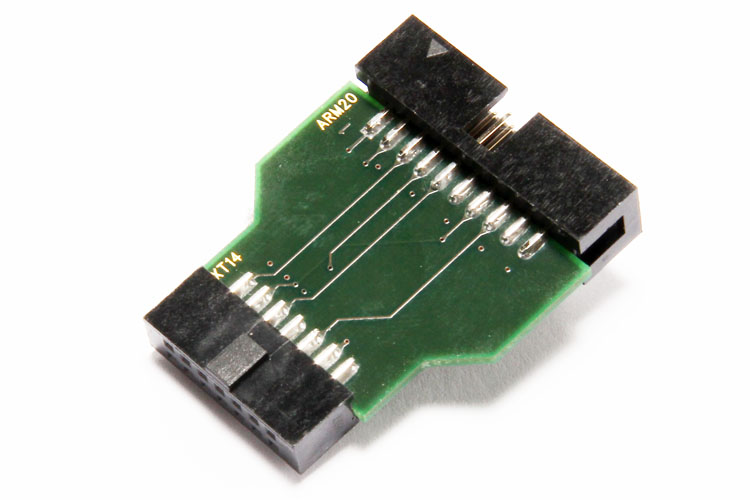

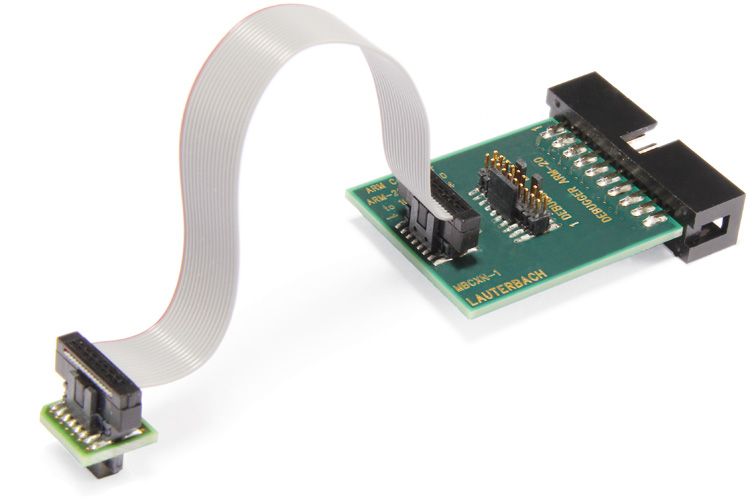

あらゆるターゲットに接続

組み込み用途で使用されるコネクタは多種多様です。当社では、使用されるコネクタに対応するコンバータを幅広く取り揃えています。

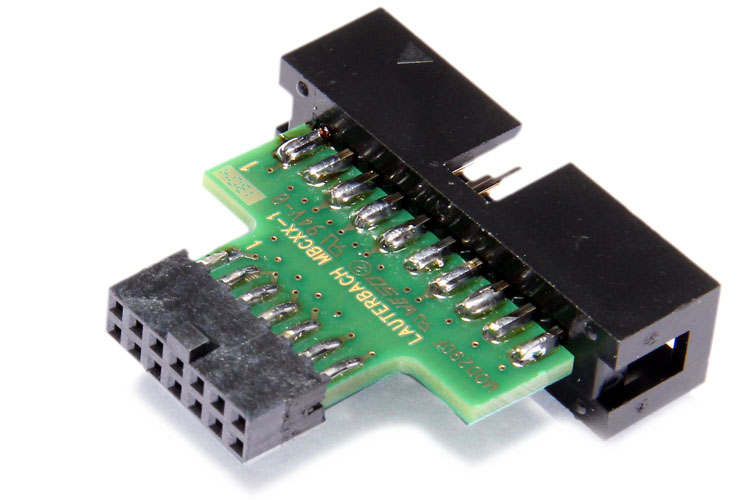

IDC20AデバッグコネクタからMIPI10またはMIPI20Tコネクタへの変換器。ローターローターバッハ 社製IDC20Aデバッグプローブをターゲット上のMIPI10またはMIPI20Tコネクタに接続するために設計されています。 MIPI20Dコネクタ(TRSTおよびRTCK付き)を搭載したボードの場合は、 代わりにコンバータLA-3770が必要です。 両コンバータの違いについては以下を参照してください: ローターバッハ 注記:このコンバータはCoreSight MIPI20Tコネクタのトレースピンを接続しません。 IDC20Aデバッグケーブルでは使用されないためです。 ただし、SWO/SWV経由のトレースはサポートされています。

IDC20AデバッグケーブルをMIPI34、MIPI20D、またはMIPI10コネクタを備えたターゲットに接続するためのコンバータ。 PowerTrace Serial でIDC20Aデバッグケーブルを接続する場合は、代わりにコンバータLA-2770PowerTrace Serial 。 (LA-2770はピン1が右側にあるMIPI34コネクタ用です。 一方、LA-3770はターゲット側でピン1が左側にあることを前提としています。) MIPI20Tコネクタ(オフチップトレース用ピン付き)搭載ボードの場合、 ドライバ競合を避けるため、代わりにLA-2729コンバータの使用を推奨します。 両コンバータの違いについては以下を参照: ローターバッハ あるいは、ドライバ競合を回避するため、 本コンバータのJ101とJ102を開いて MIPI20Tコネクタ付き基板に接続することも可能です。 詳細は以下を参照: ローターバッハ

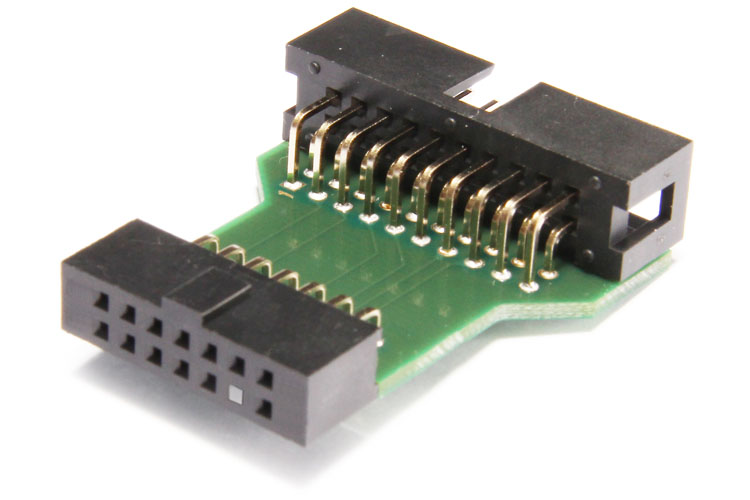

Converter to connect a Debug Cable to a TI-14 or TI-20-Compact connector which is used on many targets with processors from Texas Instruments

Converter to connect an IDC20A Debug Cable to a TI-14 connector which is used on many targets with processors from Texas Instruments

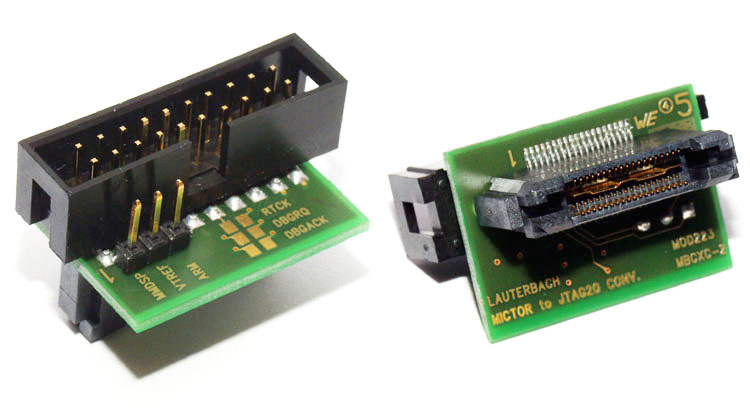

Converter to connect the IDC20A Debug Cable to a Mictor connector on the target providing both debug and trace signals. This is needed if you want to connect the Debug Cable without a Preprocessor and if there is only a Mictor on the target.

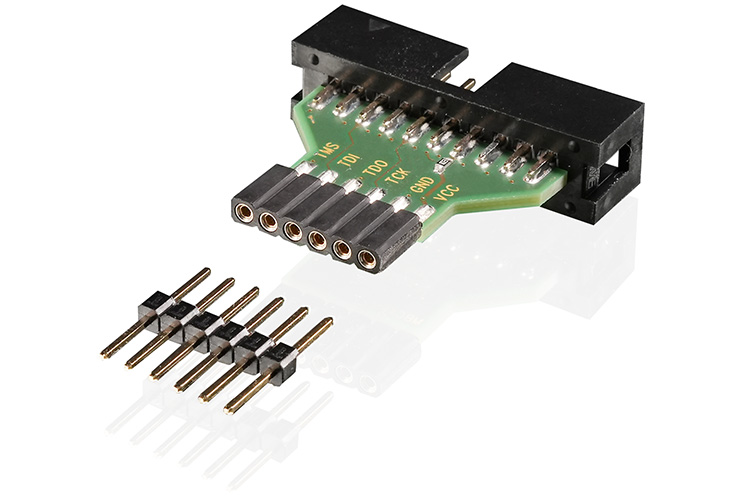

IDC20Aデバッグケーブルを標準6ピン「Pmod™」コネクタに接続するための変換アダプタ。 「Pmod™」はDigilent Inc.の商標です。

Converter to connect an IDC20A Debug Cable to a 14-pin JTAG connector on Xilinx target boards.

Converter to connect an IDC20A Debug Cable to a MIPS-14 connector on the target

Adapter to connect an IDC20A debug probe to a classic 14 pin debug connector for Xtensa.

他のデバッグプローブを探す

IDC20Aデバッグプローブが適切なソリューションでない場合は、他のさまざまなデバッグプローブをご用意しています。