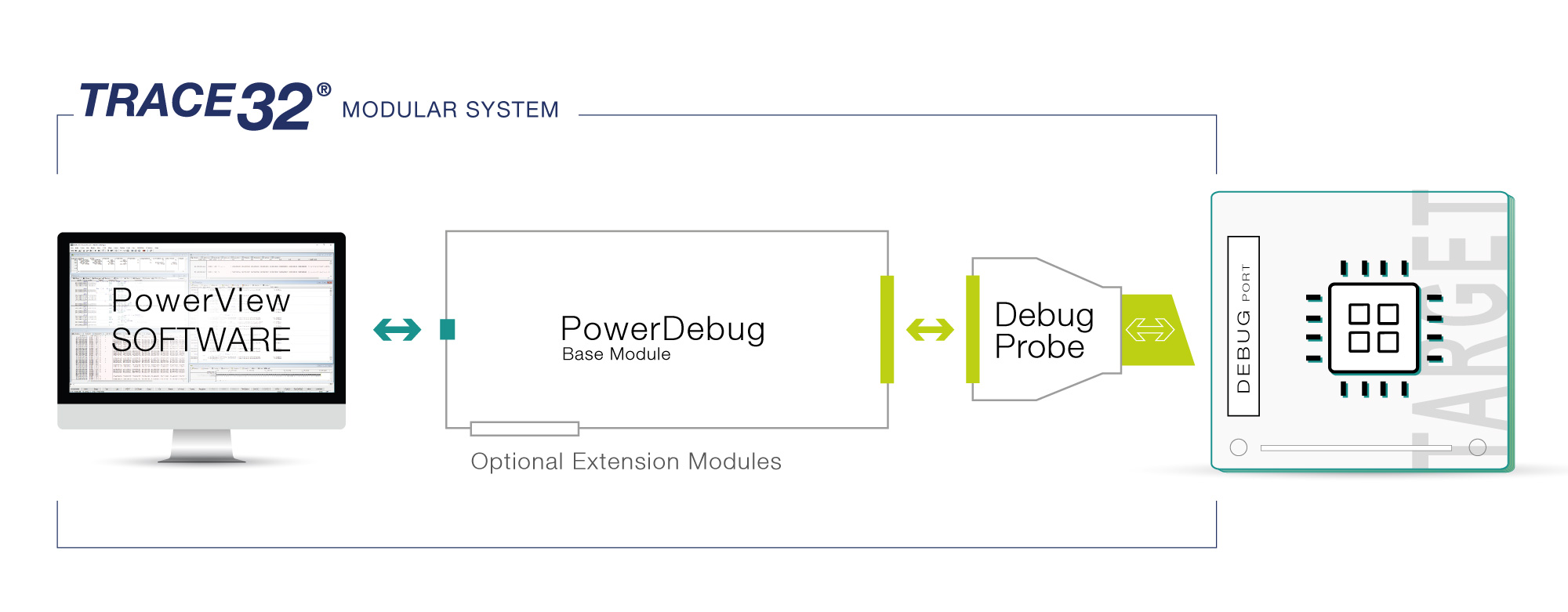

PowerDebug システム

ほとんどのチップをデバッグするための基盤

PowerDebug モジュールは専用のデバッグ・アクセラレータであり、ターゲットに近接しているため、応答時間を短縮し、アップロード/ダウンロード速度を向上させ、多くのデバッグ決定をホストからオフロードします。これにより、ホストベースのデバッグ・システムと比較してデバッグ作業が大幅に高速化し、開発期間とコストを削減します。

最高のシグナルインテグリティでターゲットに接続

ターゲットとPowerDebug モジュールの間に位置するのが、プラットフォーム固有のデバッグ・プローブです。このプローブは、電圧、信号、サポートされるプロトコル、物理的な寸法など、デバッグ・インターフェースの仕様に適応します。アクティブ回路をターゲット・プロセッサのできるだけ近くに配置することで、可能な限り高いシグナル・インテグリティを保証します。

デバッグプローブには、ターゲットプロセッサアーキテクチャ用のライセンスが含まれています。SoC内で複数のコアを同時にデバッグする場合、プローブは複数のプロセッサアーキテクチャのライセンスを取得できます。

ターゲット開発ボードや最終的なターゲットハードウェアが異なれば、メカニカルコネクタも異なる場合があります。デバッグプローブをテスト対象ユニットにマッピングするために、さまざまなアダプターとコンバーターを用意しています。

CombiProbe は、デバッグとトレースを統合した2つのポートを備えた高度なデバッグプローブです。システムトレースやコンパクトフロートレース用の4ビットトレースポートをサポートしています。さらに、ミックスドシグナルプローブを接続して、デジタルまたはアナログ信号を解析することができます。

JTAG

JTAGは、ほとんどのCPUで一般的に利用できる通信プロトコルです。元々はバウンダリー・スキャン・デバイス・テスト用に開発されたもので、JTAGによって外部ツールはチップ内部のテスト・アクセス・ポイント(TAP)コントローラと通信することができます。TAPはチップ内のデバッグインフラへのアクセスポイントです。TAPは、1つのデバッグプローブで複数のコアのデバッグを可能にするために、チェーン接続することができます。

cJTAG (IEEE 1149.7)

コンパクトJTAG(cJTAG)は、デバッガとコアのテストアクセスポイント(TAP)間のJTAG通信をシリアル化することで、デバッグインターフェイスのピン数を削減するJTAGベースの技術です。複数のチップをスター型トポロジーでサポートできます。通常のJTAGと比較して、デバッグ性能は若干低下しますが、物理ピンのコストを削減できます。

CoreSightシリアルワイヤデバッグ(SWD)

SWD(Serial Wire Debug)は、Arm®によって定義された2ピンのデバッグ・インターフェースで、CoreSight™デバッグ・インフラストラクチャに最高のパフォーマンスでアクセスできるように最適化されています。

Infineon DAP

インフィニオン・デバイス・アクセス・ポート(DAP)は、2ピン以上の多用途デバッグ・インターフェースです。CRC6保護機能により、ノイズの多い環境でも堅牢です。JTAGよりもはるかに高い周波数をサポートし、低~中帯域幅でのトレース・データ送信も可能です。

Nexus (IEEE 5001)

Nexusは組み込みプロセッサのデバッグとトレースのための標準を定義しています。最近の Nexus 準拠チップのほとんどは、デバッグ用に通常の JTAG を提供し、リアルタイムのトレースデータ送信用にのみ補助ポートを使用します。しかし、MPC56x や MP63x のようないくつかのチップは、デバッグとトレースの両方にパラレル補助ポートを全二重モードで使用します。

BDM

バックグラウンド・デバッグ・モード(BDM)は、オンチップ・デバッグ用のシリアル・シフトレジスタ・プロトコルを提供します。もともとはMotorola/Freescaleが設計したもので、NXPのColdFire、M68K、MPC55x、PowerQuiccファミリーのデバイスに使用されています。S12/S12X/S12Z デバイスで使用されるシングルワイヤ BDM もあります。

Renesas LPD/UARTモード

ローピンデバッグ(LPD)モードは、ルネサス独自のデバッグプロトコルです。LPD4(4ピン)とLPD1(1ピン)があります。LPD4モードは、低帯域幅とソフトウェアトレース(SFT)もサポートしています。シリアルフラッシュプログラミングでは、ルネサスのデバッグプロトコルはさらに非同期および同期インターフェースモード(UART / CSI)をサポートしています。

Intel® Out Of Band(OOB)Hosting DCI

Intel® DCI OOBプロトコルは、Intel® Direct Connect Interface(DCI)へのアクセスを提供し、Intel® ターゲットをデバッグします。これは、USB 3.2 Gen 2x1 ポートのピンを使用します。アーリーブートアクセスを提供します。

Andes Serial Debug Port

シリアルデバッグポートは、アンデステクノロジー社が設計したAndesCore™およびRISC-Vプロセッサ用の2線式オプションです。

Spy-Bi-Wire

Spy-Bi-Wireはテキサス・インスツルメンツ社が開発したシリアル化されたJTAGプロトコル(cJTAGに類似)で、通常のJTAGに加えて一部のMSP430マイコンで利用可能です。Spy-Bi-Wireを使用することで、4つの物理ピンが他の目的に使用できるようになります。

Spitfire

SPITFIRE™はSPIベースのシリアルプロトコルで、Microchip社製dsPIC®プロセッサを2本のワイヤでデバッグします。AUTO26デバッグプローブはdsPIC®のフラッシュメモリをプログラムするICSPプロトコルもサポートしています。

UPDI

Microchip が設計した Unified Program and Debug Interface (UPDI) は、チップのリセットピンでもある 1 つのピンを通して tinyAVR® と megaAVR® デバイスをデバッグおよびプログラムするための独自のプロトコルです。これらのデバイスはシリアル ペリフェラル インターフェース (SPI) 経由でもプログラムできます。

Renesas Single-Wire UART

RL78プロセッサは、RESETピンとTOOL0ピンを使用するUARTのような1ライン デバッグインターフェースを介してデバッグされますが、旧型の78K0Rプロセッサは追加の信号TOOL1を使用します。

eJTAG

IEEE 1149.1 JTAG仕様を拡張し、MIPSベースのプロセッサとSoCにカスタムデバッグインターフェースを提供します。

新しいテクノロジー・新興のテクノロジー

TRACE32はデバッグとツールの最前線で活躍しています。ローターバッハのエンジニアは、組み込みに関するあらゆるワーキンググループや運営委員会のメンバーでとして参加しています。これらの新しいインターフェースには、SPIデバッグ、DCI-OOB、USB経由のデバッグ、CANデバッグなどがあります。