USB経由でのデバッグ

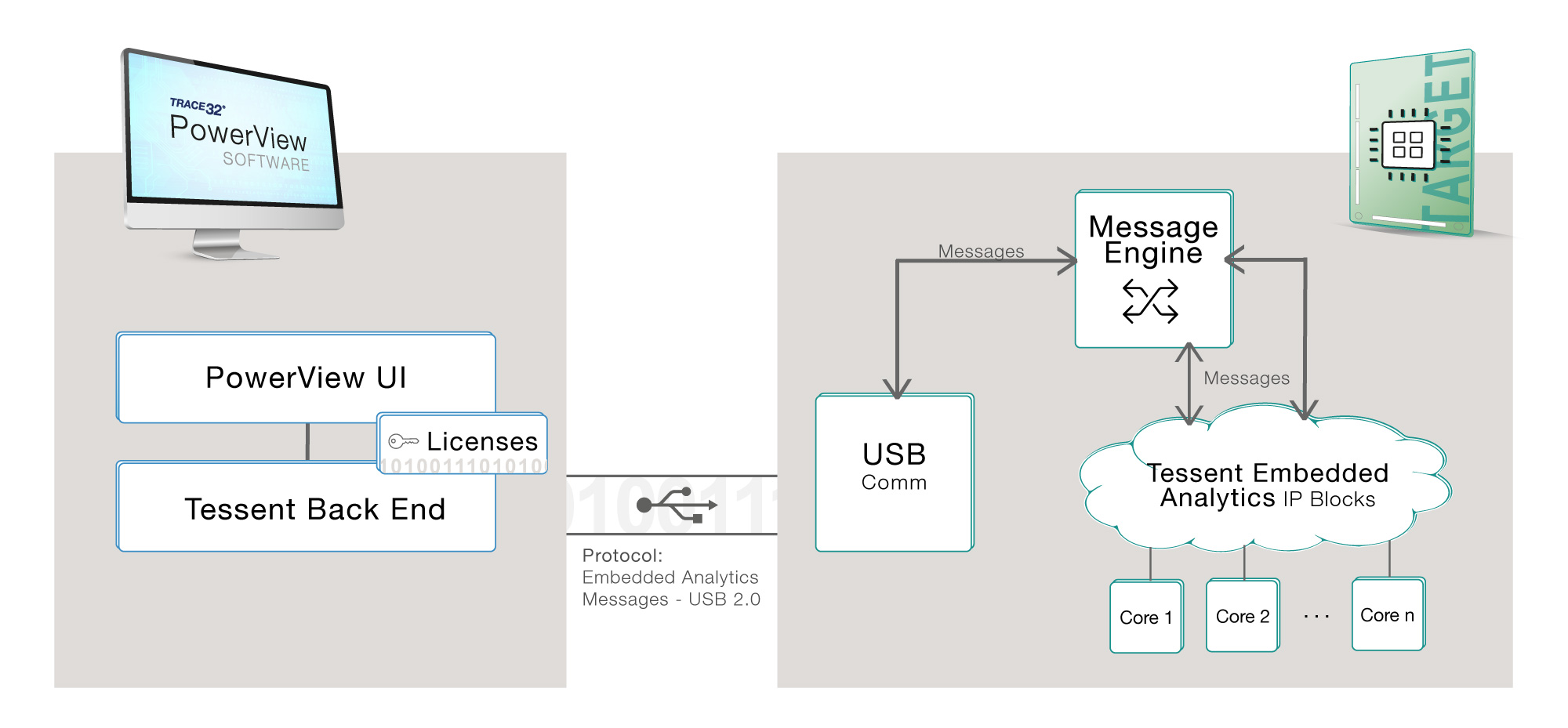

Tessent Embedded Analytics

Tessent Embedded Analytics Ecosystemは、デバッグとトレースのための分析モジュールを提供します。通信は、メッセージエンジンによってルーティングされるメッセージに基づいています。コミュニケータは、様々な物理インターフェース(その一つがUSB)を介してメッセージを送信することができます。

機能

- デバッグとトレースに必要なすべてのIPブロックをフルサポート

- USBスタック経由のストップモードデバッグ

- 同一コアと異なるアーキテクチャのコアのマルチコアデバッグ

- Linuxを含むOSを意識したデバッグ

- USBスタックによるコアトレースとバスモニタリング

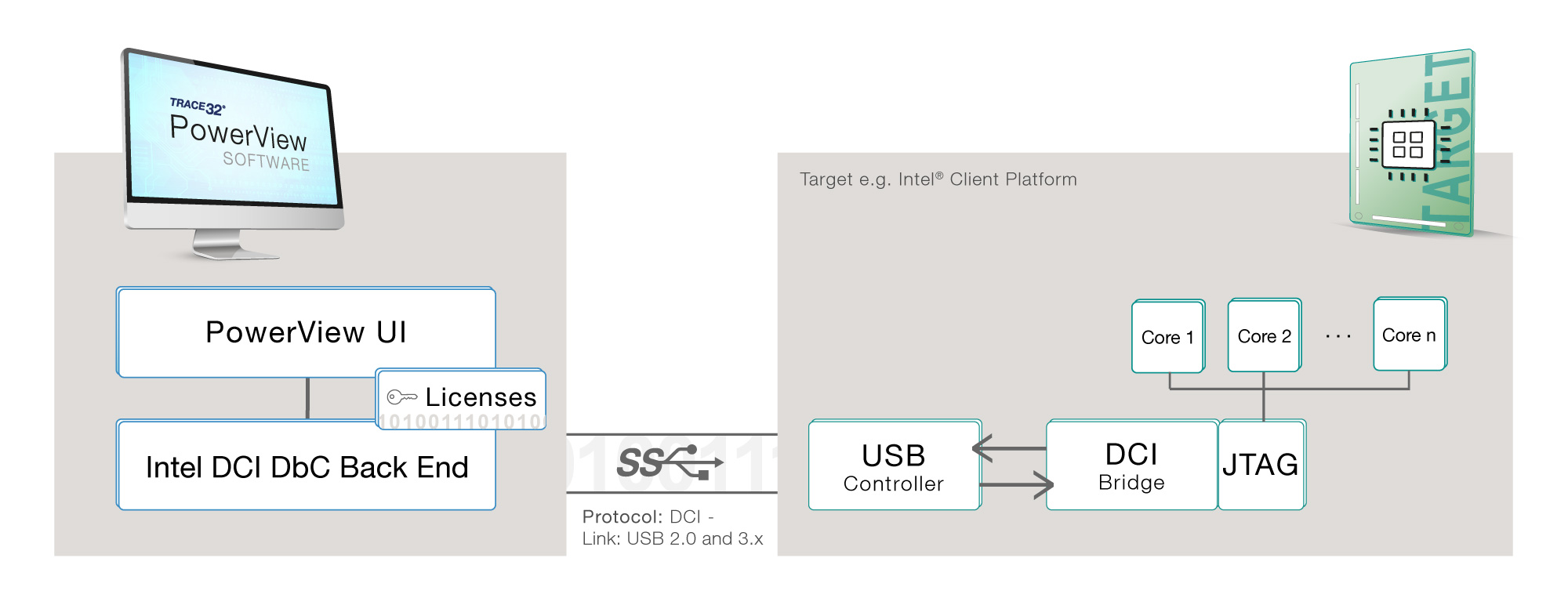

Intel Direct Connect Interface (DCI) DbC

Intel DCI DbCは、USBポート経由でインテルx86プラットフォームのデバッグを可能にします。通信インフラはJTAGに基づいています。中心的なコンポーネントはDCIブリッジで、USB経由で送られてくるコマンドに基づいてJTAGスキャンを生成します。これらのJTAGシーケンスにより、チップの内部テストアクセスポート(TAP)だけでなく、外部接続されたJTAGデバイス(クライアントやサーバーシステムのCPUなど)にもアクセスできます。

機能

- USBスタック経由のストップモードデバッグ

- 同一コア(ハイパースレッディングを含む)と異なるアーキテクチャのコアのマルチコアデバッグ

- すべてのUEFIフェーズ用のテーラーメイドGUIによるBIOS/UEFIデバッグ

- LinuxおよびWindowsに対応したデバッグ

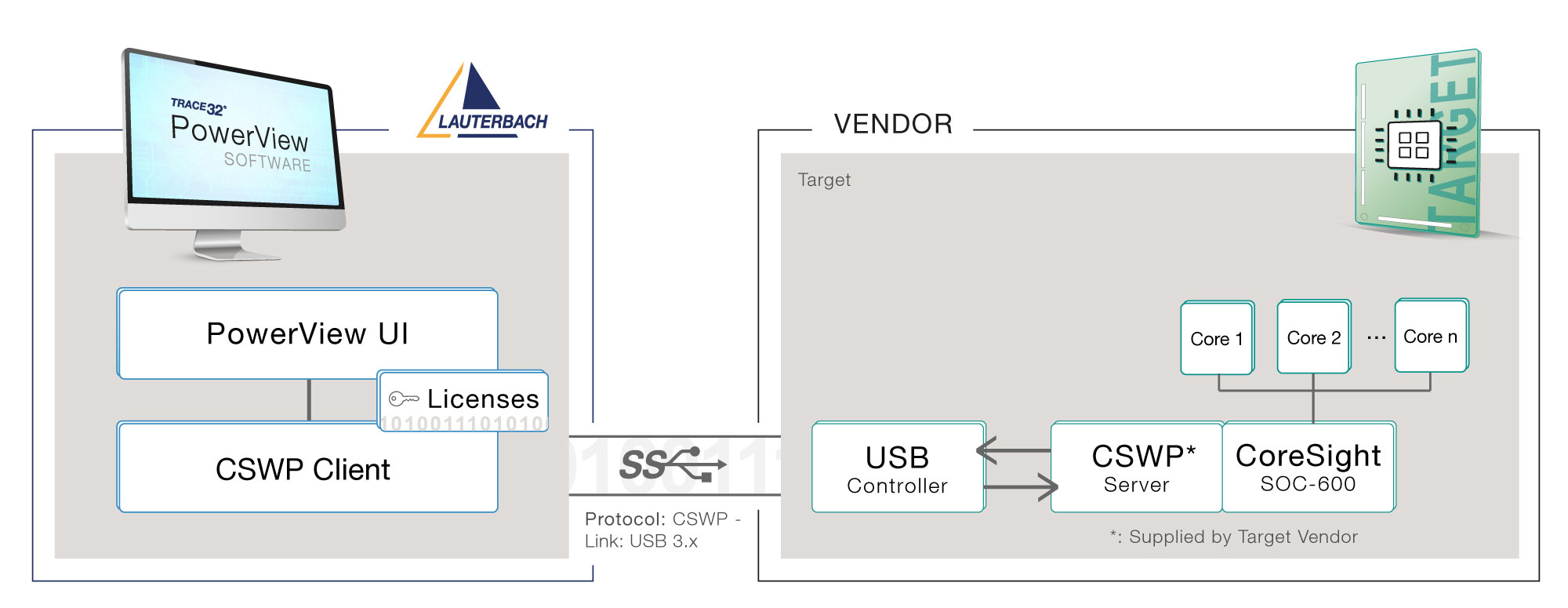

Arm CoreSight Wire Protocol (CSWP)

Arm CSWPプロトコルは標準化されたトランスポートプロトコルであり、物理リンクに依存しません。Arms CoreSight SoC-600 IPを実装することで、SoCはデバッグメモリ空間へのアクセス標準と、高帯域幅ストリーミングトレースモードをサポートする拡張組み込みトレースルーター(ETR)を活用することができます。SoCとPowerView 間の通信は、チップ上に実装されたCSWPサーバーによって制御されます。

機能

- デバッグとトレースに必要なすべてのIPブロックをフルサポート

- USBスタック経由のストップモードデバッグ

- 同一コアと異なるアーキテクチャのコアのマルチコアデバッグ

- Linuxを含むOSを意識したデバッグ

- USBスタックによるコアのトレース