Xtensaデバッガとトレース

The Perfect Solution for Debugging Xtensa Cores Across Diverse SoC Designs

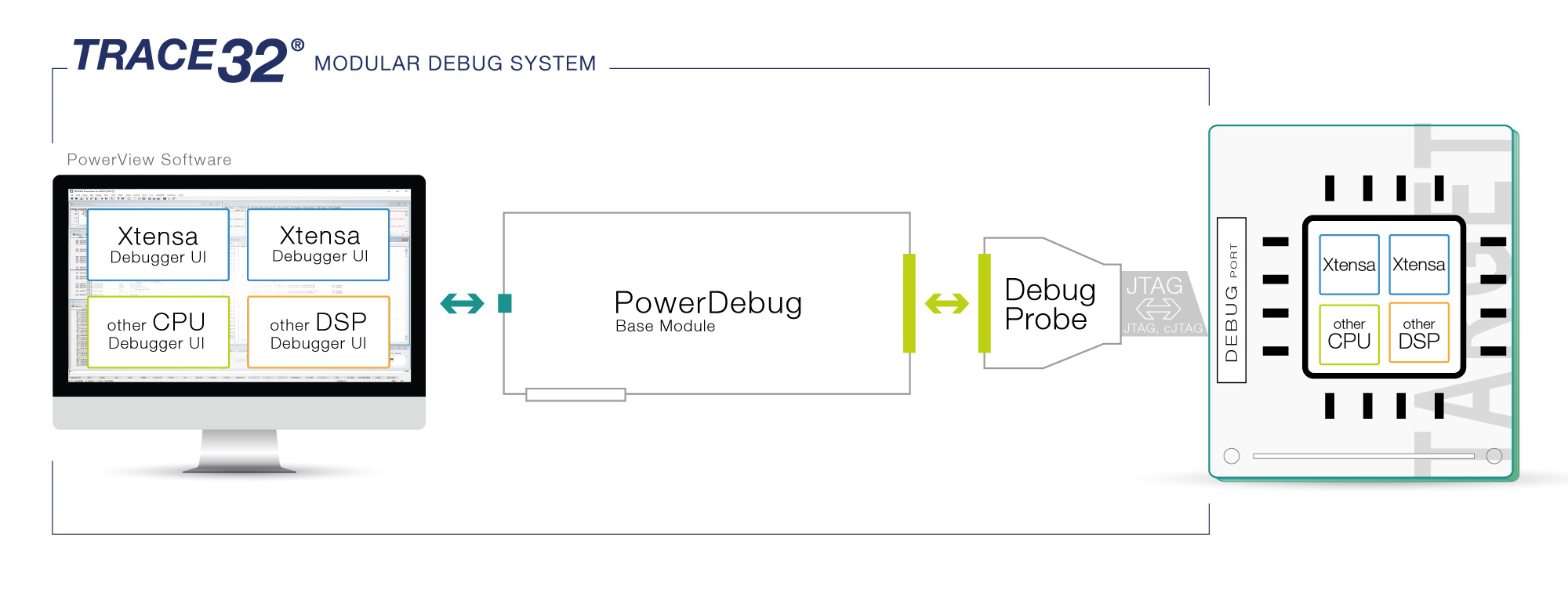

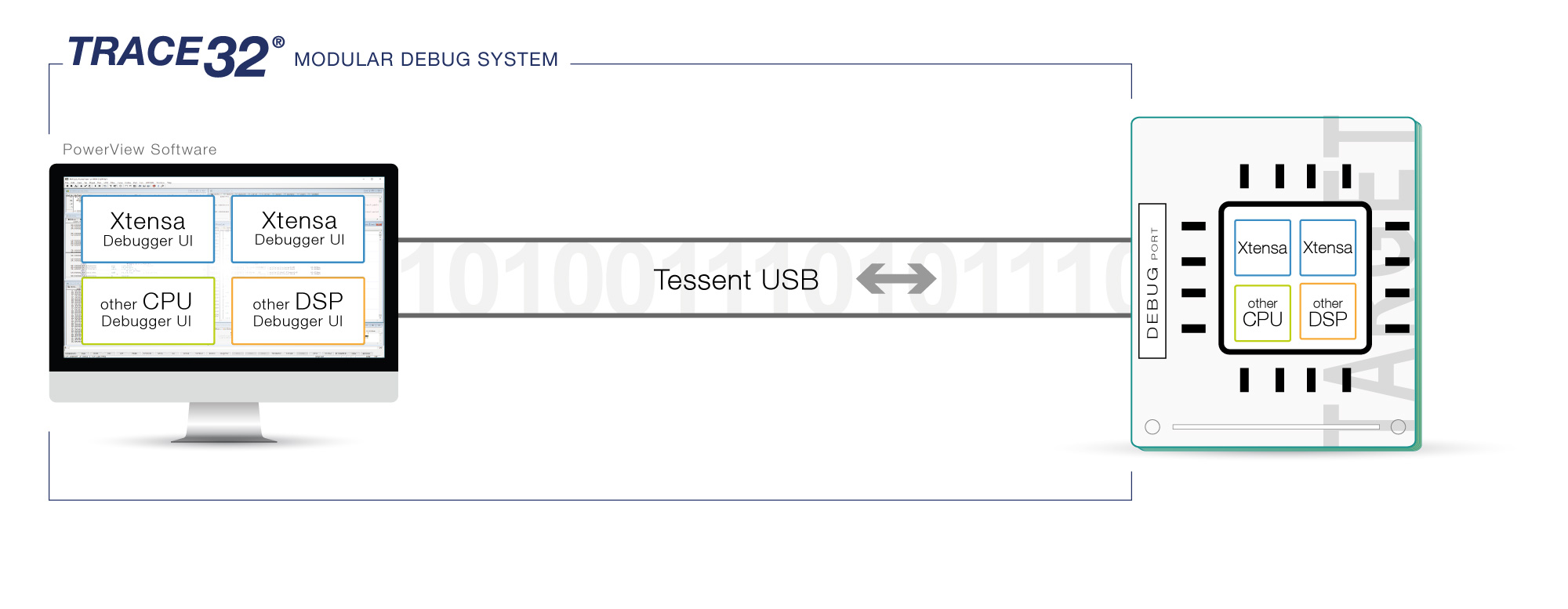

Xtensaは、Cadenceが提供するコンフィギュラブルなプロセッサIPであり、システム設計者は、サイズの変更や機能の選択、新しい命令の追加によって、組み込みアプリケーションに最適化することができます。世界をリードするTRACE32®ツールを使用すると、単一のデバッグインターフェイスを介して、SoC内の様々なXtensaコア(他の全てのコアも含む)を同時にデバッグし、制御することができます。TRACE32®は、小規模な組込みコントローラから大規模なマルチコアデータ処理エンジンまで、あらゆるレベルのアプリケーションをサポートします。

対応サブアーキテクチャ

Xtensa® LX4/LX5/LX6/LX7/LX8, Xtensa® NX

すべてのデバッグ機能を活用する

ローターバッハのデバッグモジュールは、オンチップブレークポイントのフルサポート、フラッシュプログラミング、ベンチマークカウンタ、キャッシュビューなど、Xtensaコアのパワフルで有名な機能をすべて利用できます。もちろん、すべてがスクリプト化できるので、同じテストシーケンスを何度も繰り返すことができます。

デバッグシステムの詳細

どのXtensaコアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

コアのアクションを捉える

ストップモードデバッグは強力なツールですが、トレースはさらに有効です。Xtensaのトレースソリューションは、NEXUS-5001互換のTRace Analyzer for Xtensa (TRAX)とオフチップトレースの両方をサポートしています。TRAXはライセンスフリーで、生成されたトレース情報をユーザ設定可能なオンチップメモリバッファに保存します。オフチップトレースソリューションは、データ収集能力が大幅に向上し(最大8GByte)、Arm CoreSightトレースストリームにTRAXパケットを埋め込むことができます。このように使用することで、コア間のトレース相関を実行することができます。

*タイムスタンプはXtensaコア内で設定する必要があります。

どのXtensaコアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

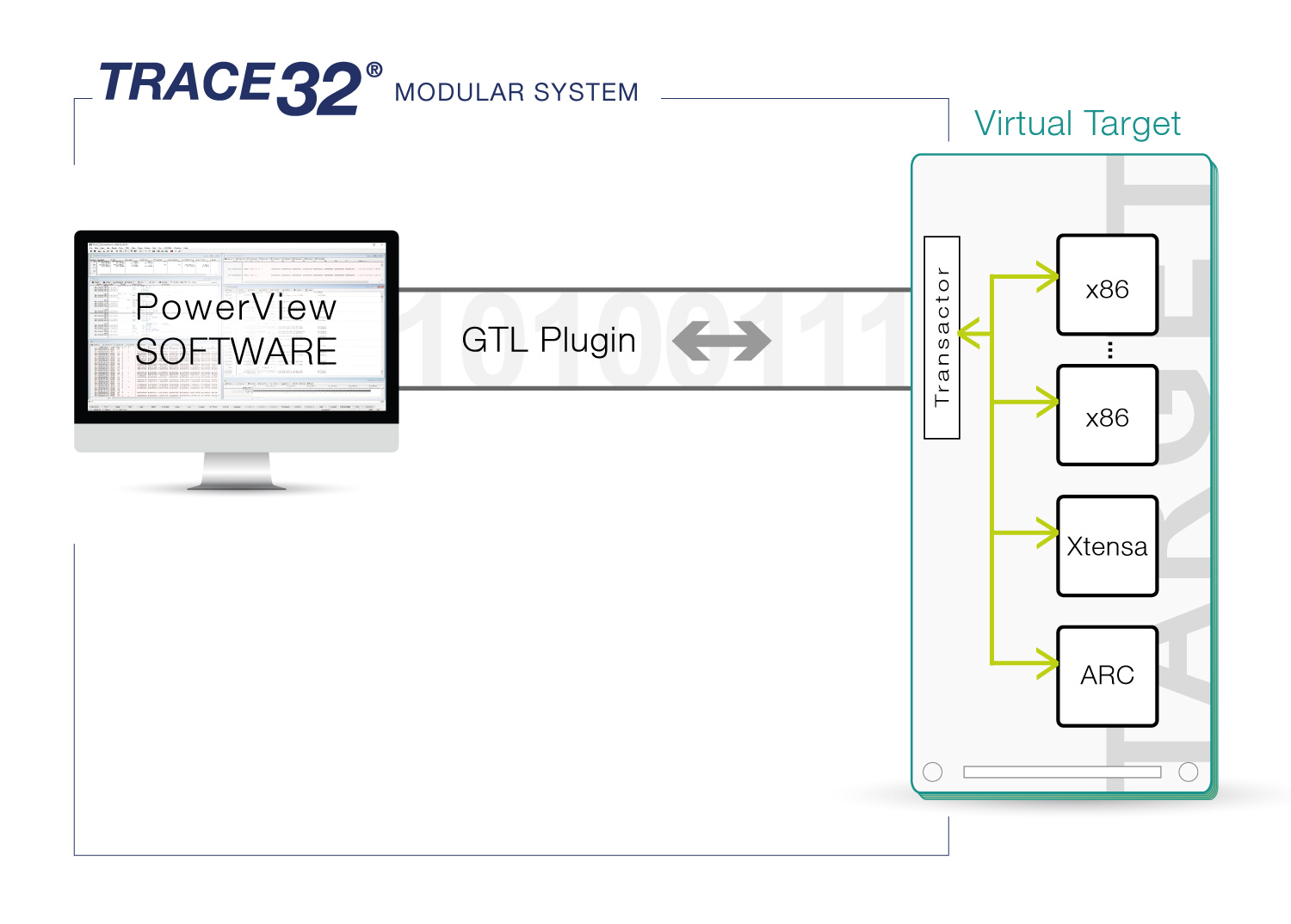

シリコンの前に準備を整えよう

SoCが完成する前に、XtensaのコードをカスタムSoCでテストできます。SoCのテーピングには多くの時間がかかりますが、TRACE32 、仮想プロトタイプやシミュレータ上でソフトウェア開発を始めることができます。

シミュレートしたVerilogまたはVHDLネットリストを使用して、テーピング・アウト前にデバッグ・メカニズムを含むSoCを検証します。ローターバッハ Generic Transactor Library (GTL)を使用することで、レジスタレベルでプレシリコンデバッグを行うことができます。

Xtensa対応のサードパーティツール

以下の機能は、TRACE32 がサポートするすべてのアーキテクチャで利用可能です。お使いのデバイスやツールがここに掲載されていない場合は、お問い合わせください。