RISC-V®デバッガ&トレース

あらゆるチップのあらゆるRISC-Vコア

RV32を使用した小さなマイクロコントローラからRV64を使用した巨大なマルチコアアプリケーションプロセッサまで、RISC-V命令セットアーキテクチャ(ISA)を実装したあらゆる設計を最先端の開発ツールで解析できます。

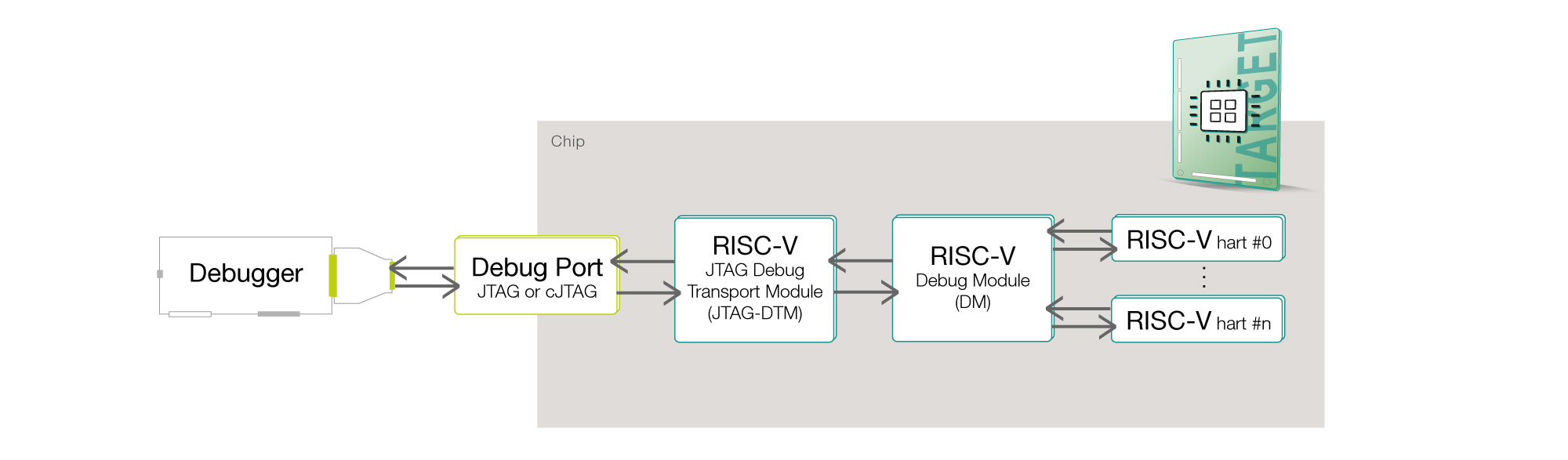

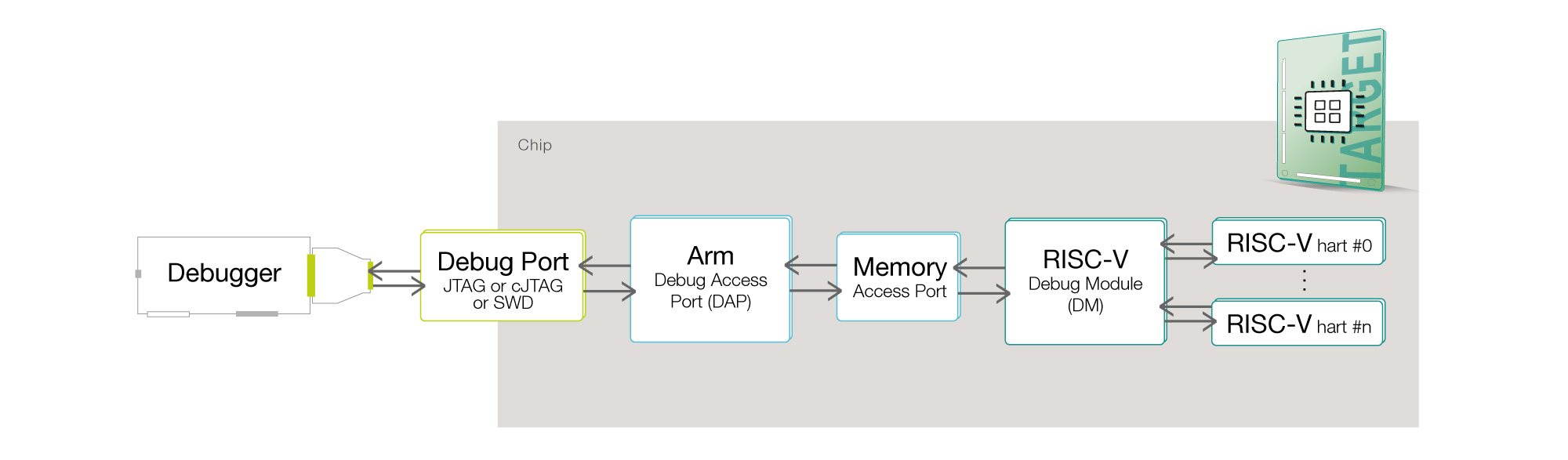

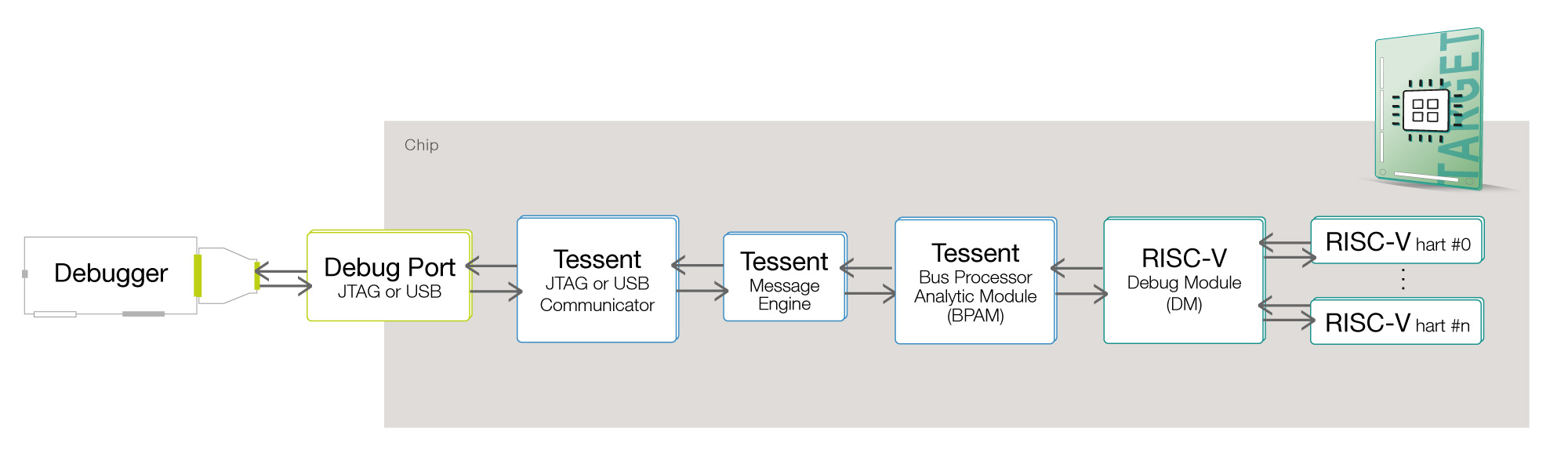

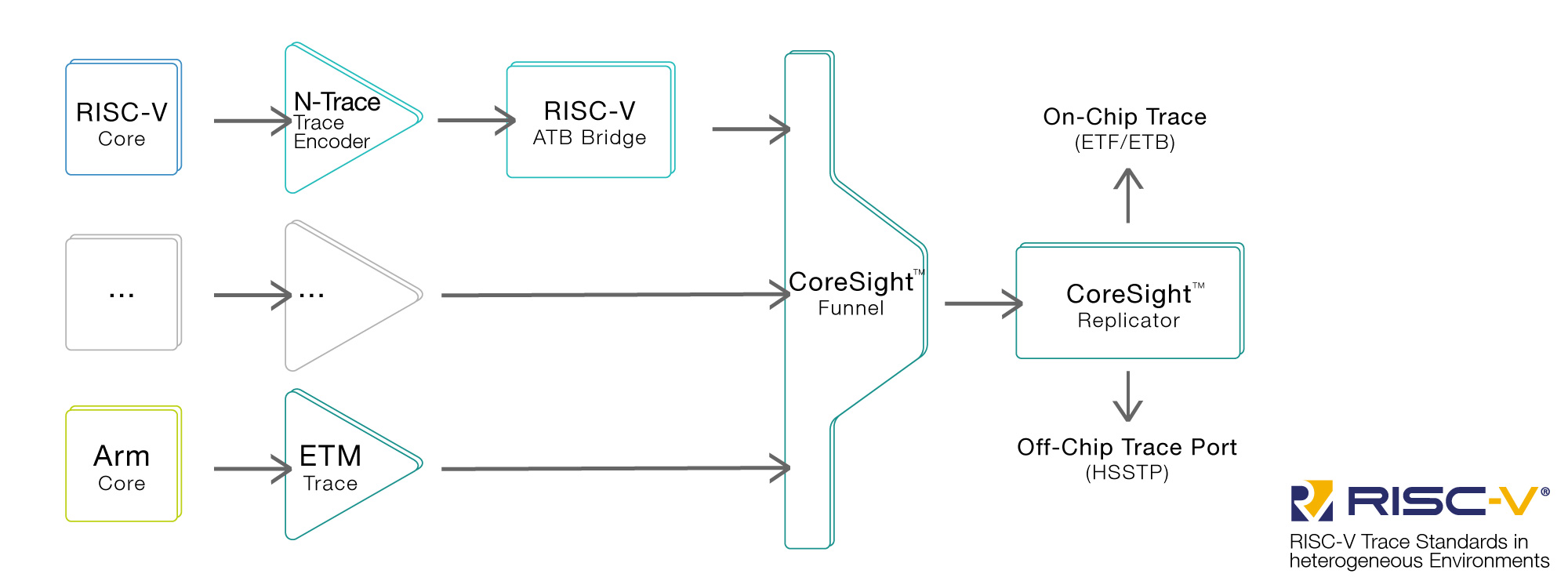

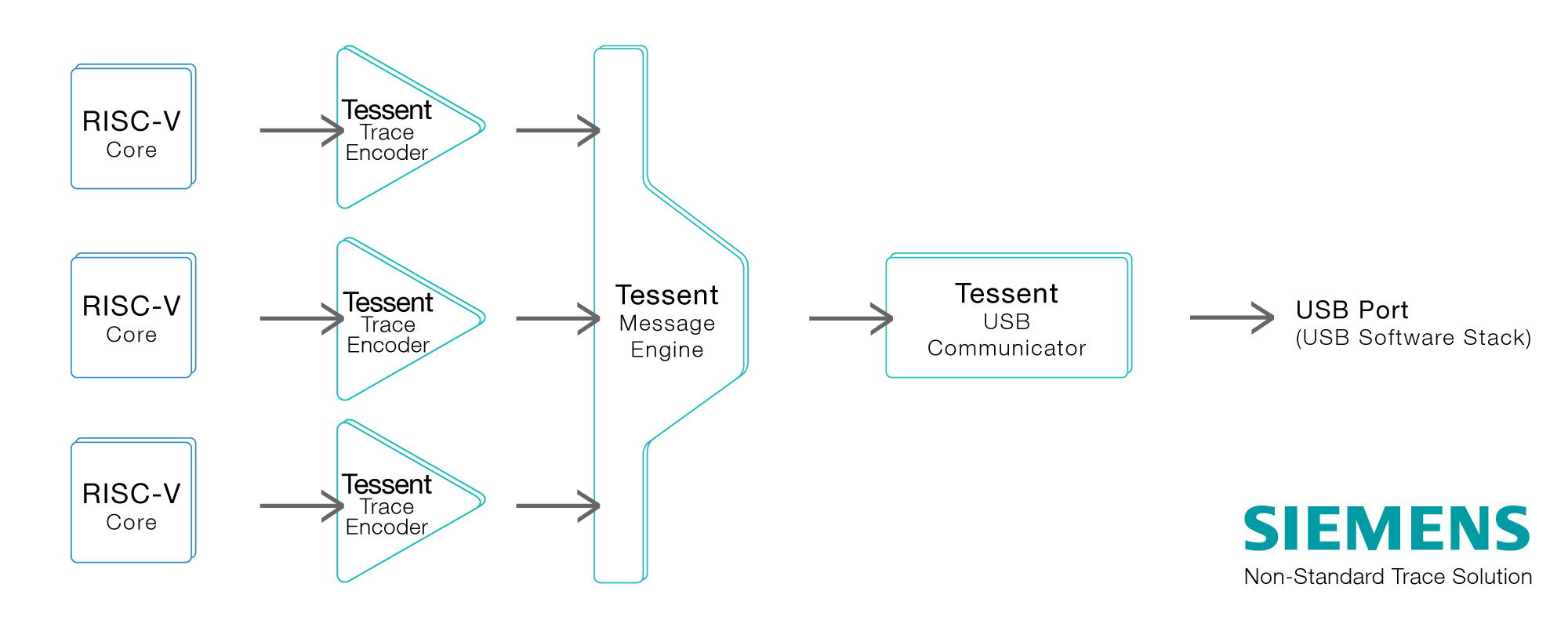

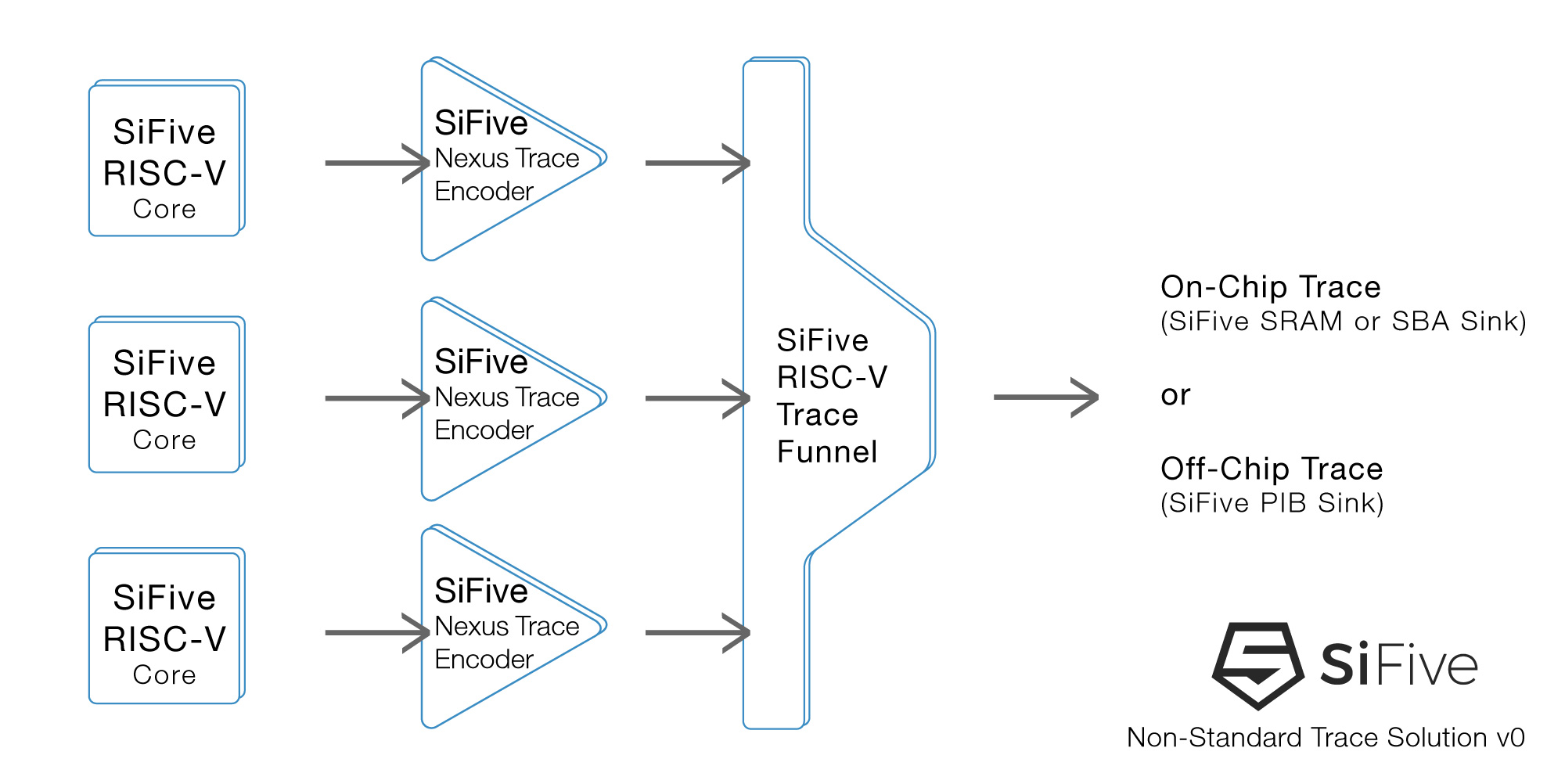

当社のTRACE32® ツールを使用することにより、SoC内の全てのRISC-Vコア(他の全てのコアも含む)を単一のデバッグインタフェースで同時にデバッグ及び制御することができます。TRACE32®ツールは、全ての主要なRISC-Vトレースシステムのオンチップ及びオフチップトレースをリアルタイムにサポートします。

当初から当社はRISC-V財団の戦略的メンバーであり、RISC-V ISAを実装するほぼすべての今日のチップをサポートしてきました。RISC-Vプロセッサの設計者や半導体メーカーとの長年にわたる緊密なパートナーシップのおかげで、将来のチップ開発にも当初から対応することができ、お客様の将来性のある投資をお約束します。

対応サブアーキテクチャ

RISC-V 32ビット/64ビット、AndesCore™ V5、ARC-V™、MicroBlaze™ V、Nios® V、SiFive®コアIP

すべてのRISC-V ISA拡張のすべてのデバッグ機能を利用する

当社の強力なデバッグモジュールを使用することで、浮動小数点、圧縮命令、ベクトル演算、アトミック命令、整数乗算、さらにはカスタムISA拡張など、あらゆるISA拡張を含むRISC-Vコア設計に当社のフルデバッグ機能セットを適用できます。完全なオンチップブレークポイントサポート、ランタイムメモリアクセス、フラッシュプログラミング、ベンチマークカウンタを利用できます。すべてがスクリプト化可能であるため、テストの自動化が非常に簡単です。

デバッグシステムの詳細どのRISC-Vコアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

各RISC-Vチップのコア動作をキャプチャする

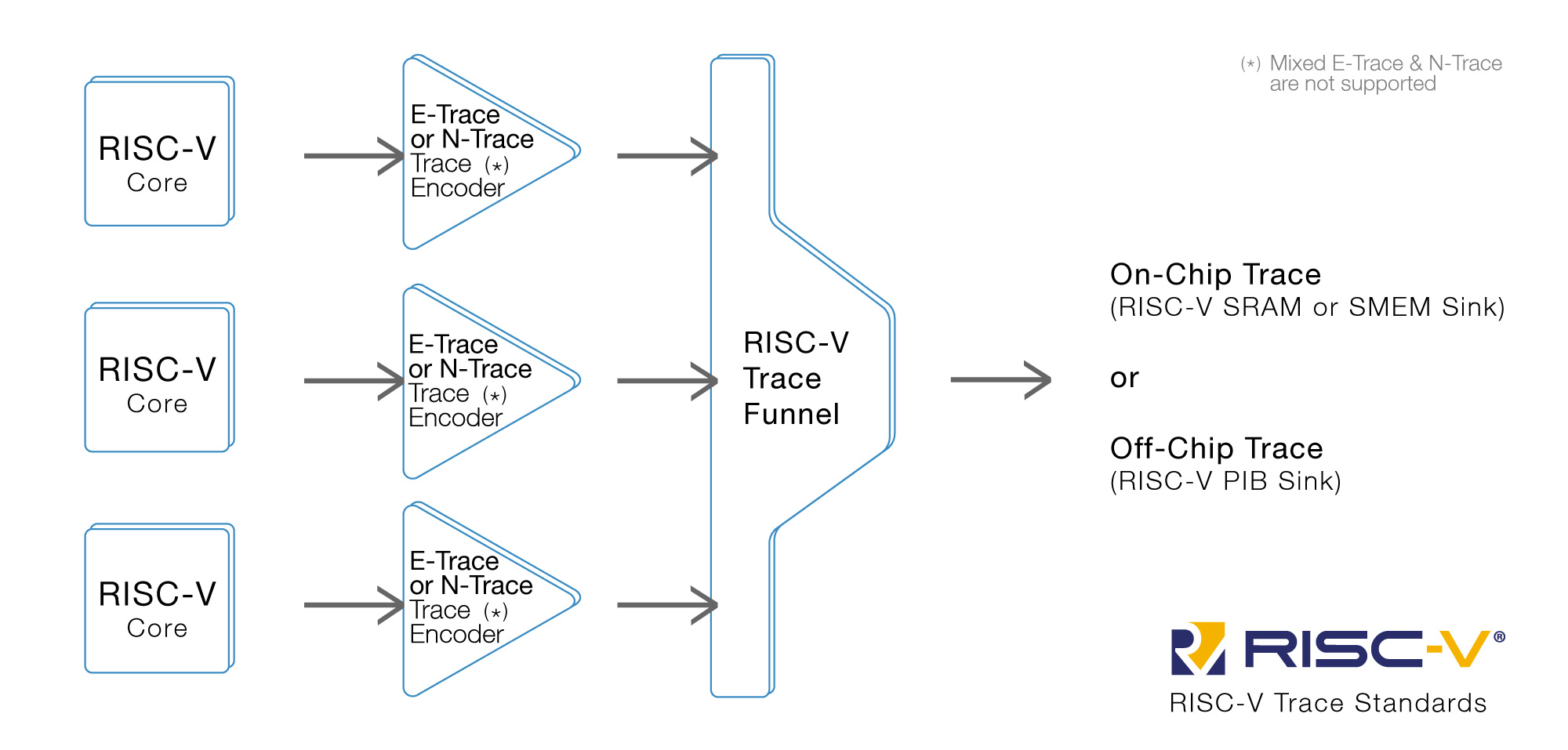

ストップモードデバッグは強力なツールですが、トレースはさらに優れています。当社のRISC-V向けトレースソリューションは、様々な技術に対応したオンチップトレースと、より強力なオフチップトレースの両方をサポートしており、トレースデータをターゲットメモリ内に保存したり、当社のPowerTraceツールのいずれかに出力したりすることができます。

どのRISC-Vコアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

シリコンの前に準備を整えよう

SoCが完成する前に、カスタムSoCでRISC-Vコードをテストできます。SoCのテーピングアウトには多くの時間がかかりますが、TRACE32 、仮想プロトタイプやシミュレータ上で、後で実際のチップで使用するのと同じGUIやツールセットを使ってソフトウェア開発を開始することができます。また、テーピングアウトを始める前に、個々のSoCのデバッグインターフェースを検証することもある程度可能です。

RISC-V対応のサードパーティツール

以下の機能は、TRACE32 がサポートするすべてのアーキテクチャで利用可能です。お使いのデバイスやツールがここに掲載されていない場合は、お問い合わせください。