ARCデバッガ&トレース

あらゆるSoCのあらゆるARCコア

Benefit from Lauterbach’s leading edge development tools and close partnership with Synopsys to analyze any design, from a single tiny microcontroller to a massive multicore application processor. ARC DesignWare® is a processor IP from Synopsys which can be optimized to fit your System on Chip (SoC).

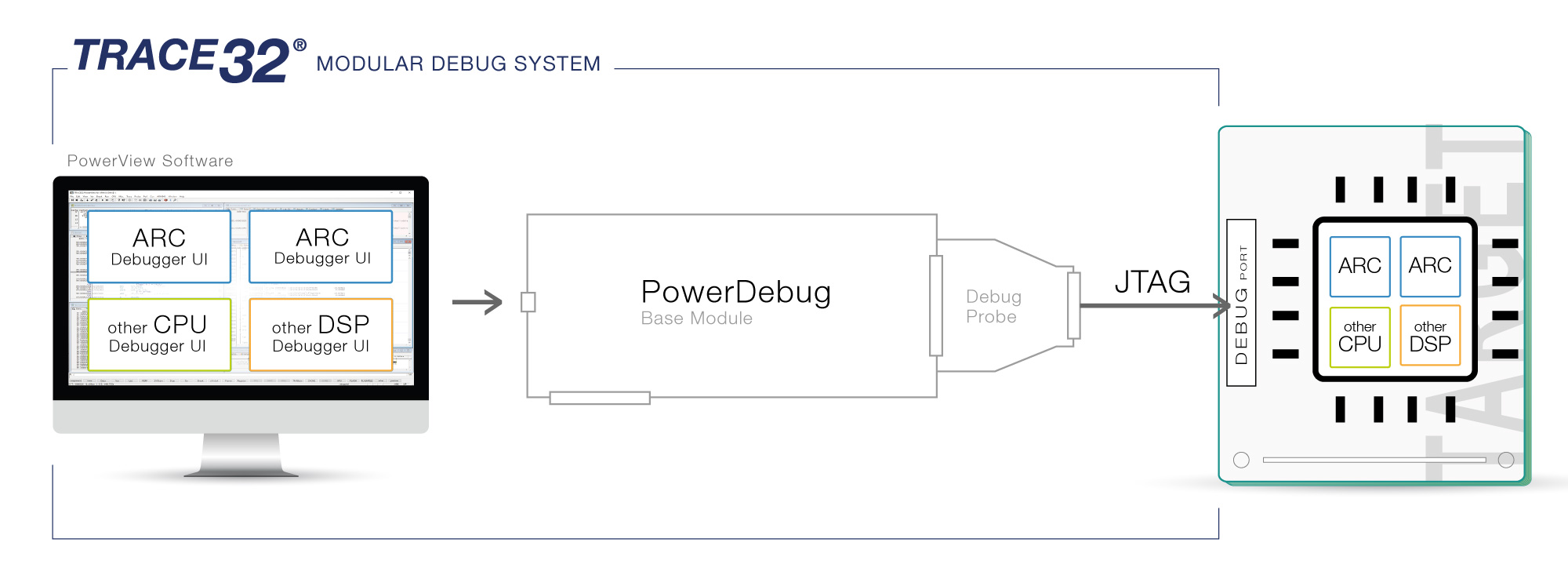

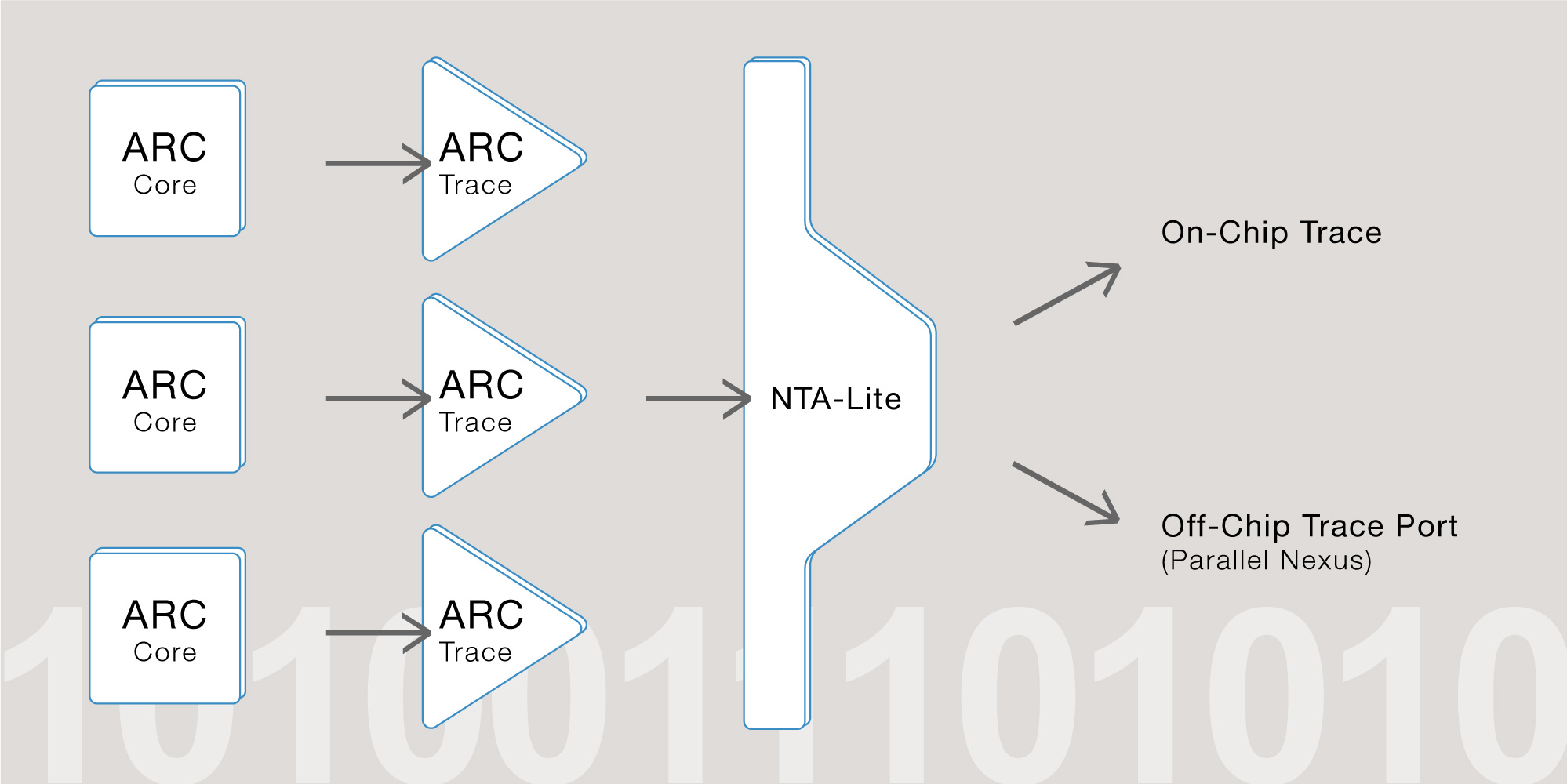

TRACE32®ツールを使用することで、SoC内の全てのARCコア(他の全てのコアも含む)を単一のデバッグインターフェイスで同時にデバッグし、制御することができます。コアのコンフィギュレーションは、ほとんどのARC Designwareのオプション機能を含めて自動的に検出されます。ARCトレース(RTT)を実装したコアの場合、TRACE32®ツールはオンチップとオフチップのリアルタイムトレースをサポートします。

対応サブアーキテクチャ

ARC-HS, ARC-EM, ARC-EV, ARC-VPX, ARC600/700, ARCtangent-A4/A5

Do you want to debug ARC-V?

For debugging ARC-V™ cores like ARC RMX, ARC RHS, or ARC RPX, please see our solutions for RISC-V.

すべてのデバッグ機能を活用する

ローターバッハのオンチップブレークポイントのフルサポート、ランタイムメモリーアクセス、フラッシュプログラミング、ベンチマークカウンター、キャッシュビューなど、ARCコアの強力でよく知られた機能をすべて探求し、活用できます。もちろん、すべてがスクリプト化可能で、同じテストシーケンスを何度も繰り返すことができます。

デバッグシステムの詳細どのARCコアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

コアのアクションを捉える

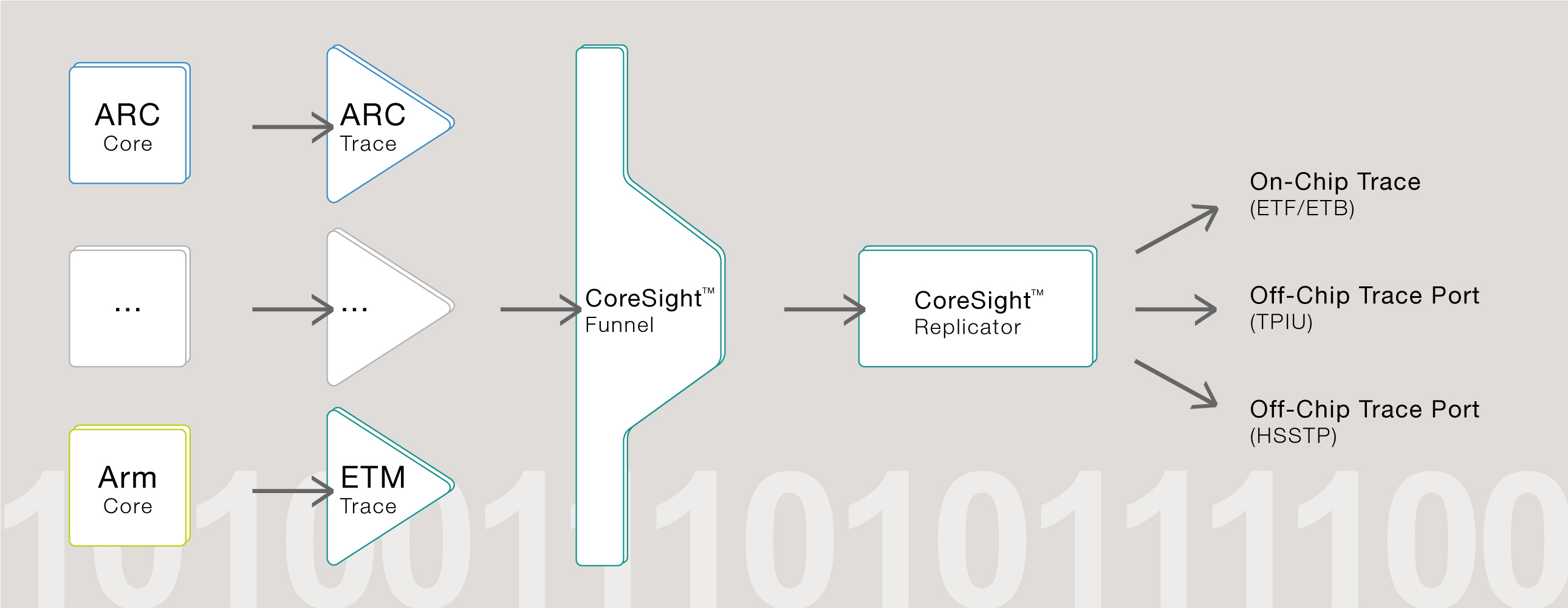

ストップモードデバッグは強力なツールですが、トレースはさらに優れています。当社のARC向けトレースソリューションは、SmaRTオンチップトレースと、より強力なDesignWare ARCトレースの両方をサポートしており、トレースデータをターゲットメモリ内に保存するか、当社のPowerTraceツールのいずれかに出力することができます。TRACE32®ツールは、Arm CoreSightトレースインフラストラクチャ内のARCトレースもサポートしています。

どのARCコアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

シリコンの前に準備を整えよう

SoCが完成する前に、カスタムSoCでARCコードをテストできます。SoCのテーピングアウトには多くの時間がかかりますが、TRACE32 、仮想プロトタイプやシミュレータ上で、後で実際のチップで使用するのと同じGUIやツールセットを使用してソフトウェア開発を開始することができます。また、テーピングアウトを開始する前に、個々のSoCのデバッグインターフェースを検証することもある程度可能です。

ARC対応のサードパーティツール

以下の機能は、TRACE32 がサポートするすべてのアーキテクチャで利用可能です。お使いのデバイスやツールがここに掲載されていない場合は、お問い合わせください。