Arm®デバッガ&トレース

Arm®の総合的なデバッグ&トレース

Arm® IPは、考えられるほとんどすべての組み込み設計で世界中で使用されています。RISCベースの命令セットは、従来のアーキテクチャよりも低消費電力、低発熱、低シリコンコストに適しており、モバイルやバッテリー駆動のアプリケーションに最適です。包括的なデバッグコア、高速トレースインターフェース、多数の相互接続、設計の柔軟性を特長とし、システムオンチップ(SoC)やシステムオンモジュール(SoM)設計のデファクトチョイスとなっているのも不思議ではありません。

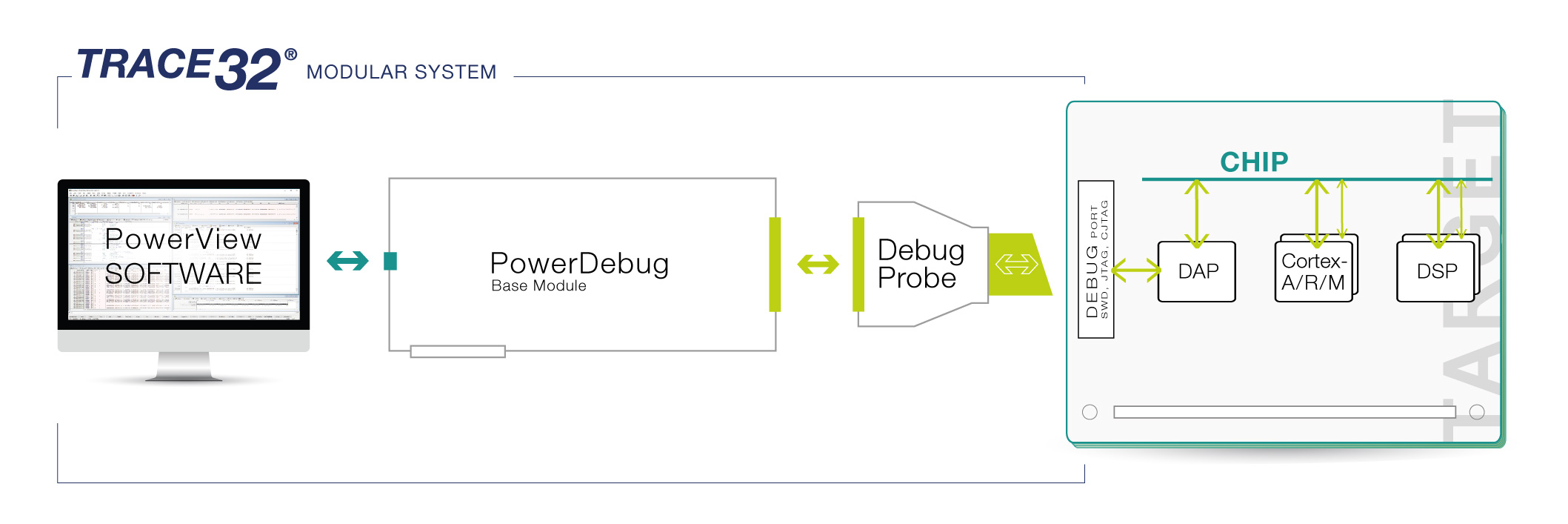

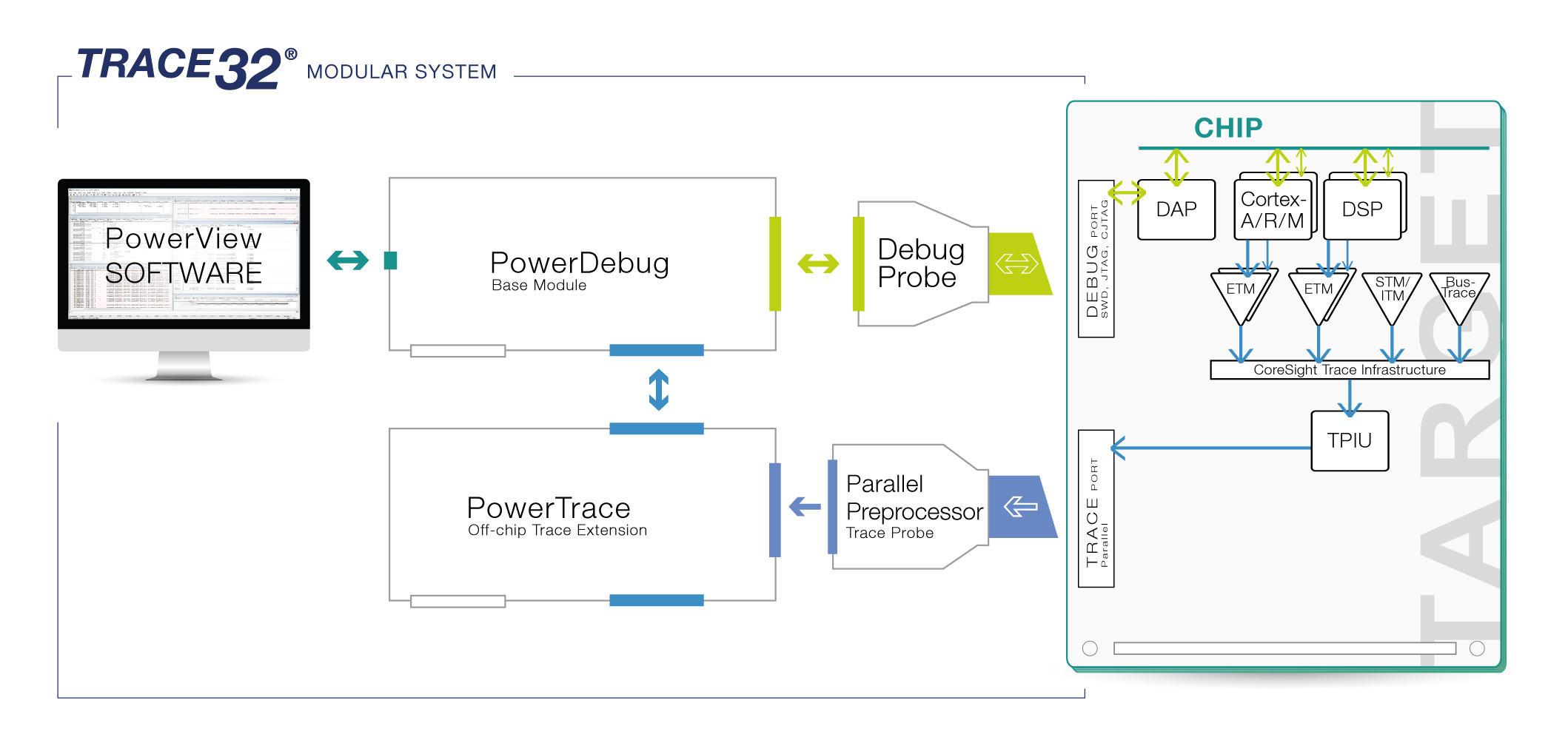

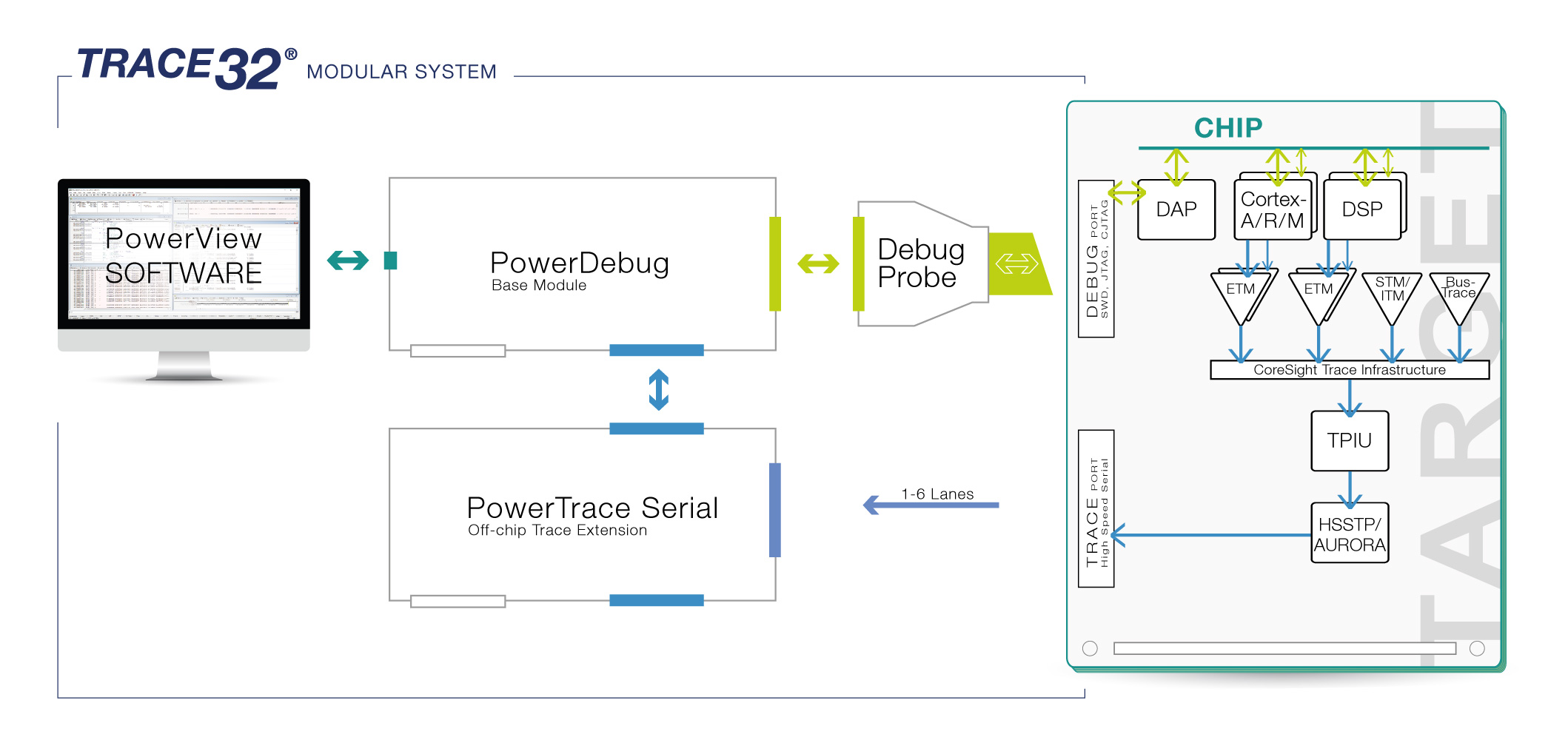

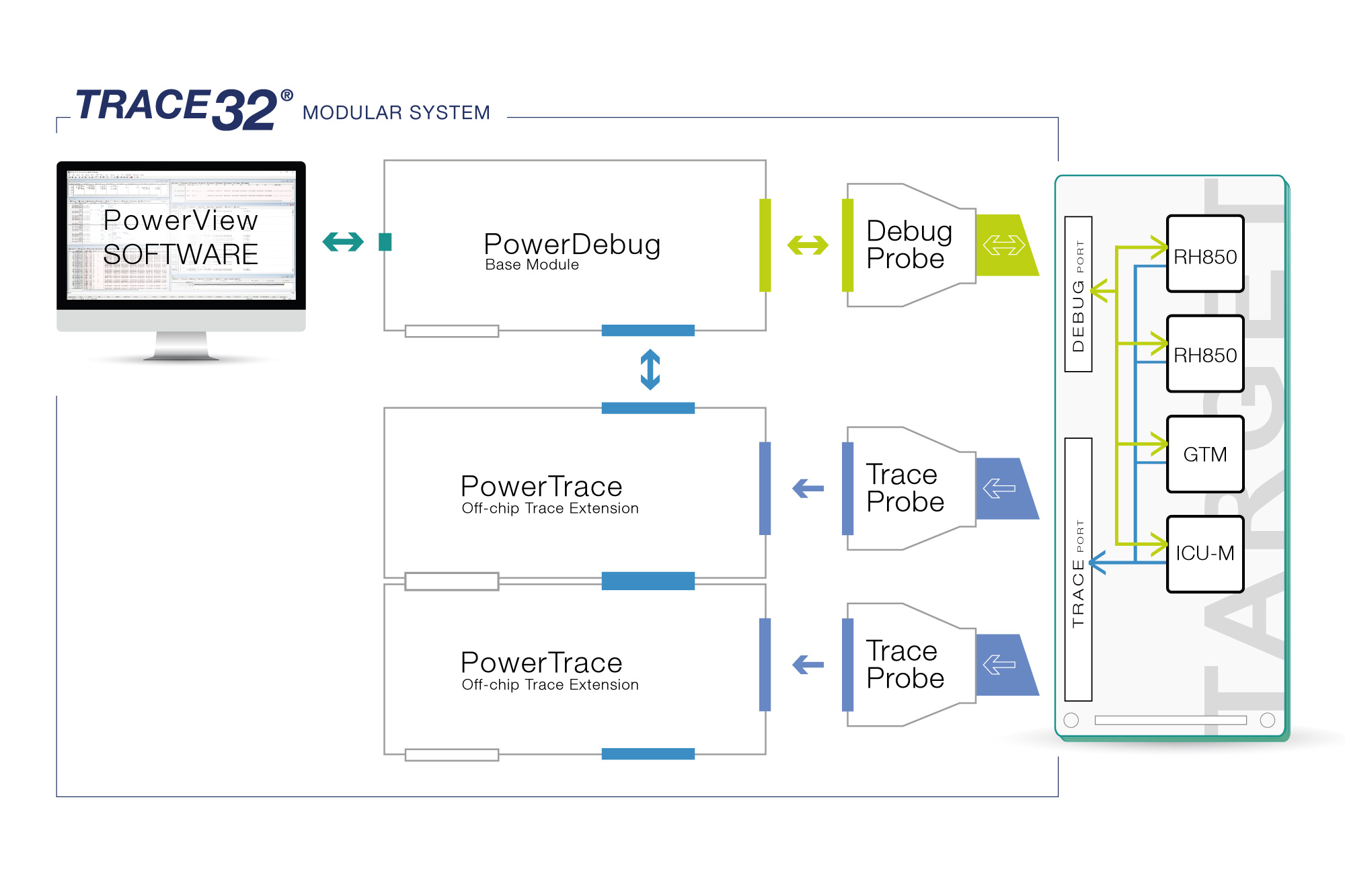

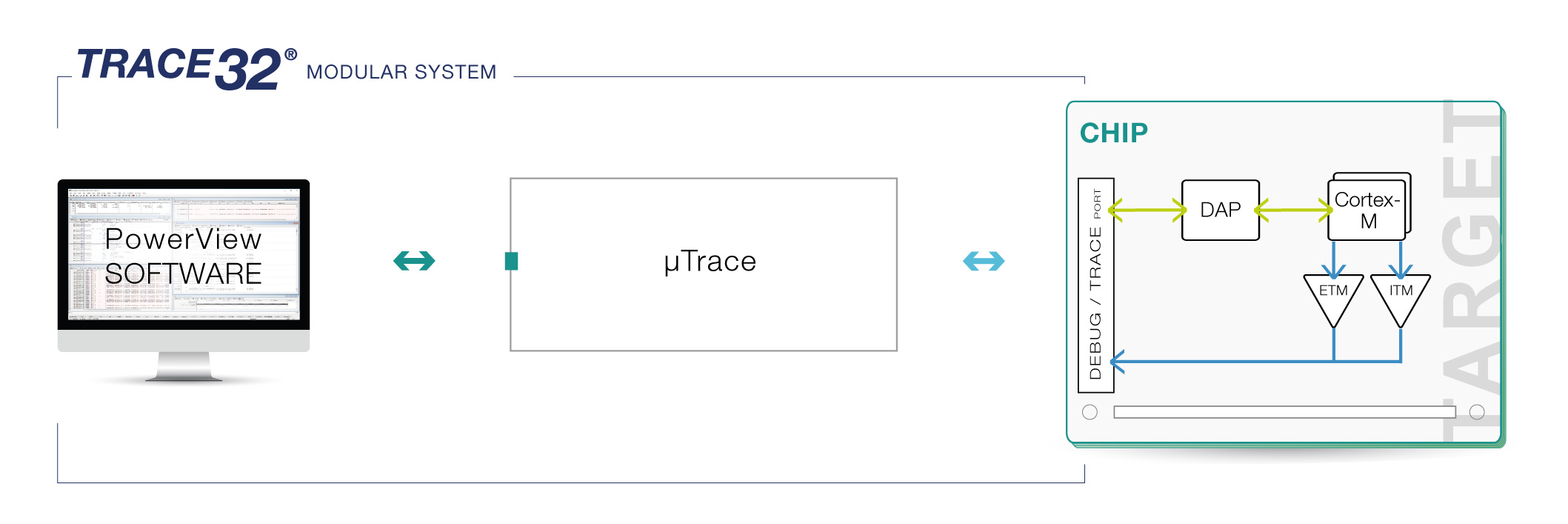

TRACE32 は、Cortex-Mデバッグおよびトレース用の低価格なµTraceから、高速オフチップ・パラレルTPIUまたはシリアルHSSTPトレースをキャプチャするためのフラッグシップツールPowerTrace III およびPowerTrace Serial ファミリーまで、Arm®ベースのマイクロプロセッサ用の完全なツールスイートを提供します。これらのツールはすべて、比類のないレベルのデバッグ機能を提供し、Arm®ベースの組み込み設計を最大限に活用できます。

対応サブアーキテクチャ

Arm®v9/v8/v7/v6, Cortex®-M/R/A/X, C1, ARM7/9/11, SecurCore®, Neoverse™, Kryo™

高速SoCをより詳細に理解する

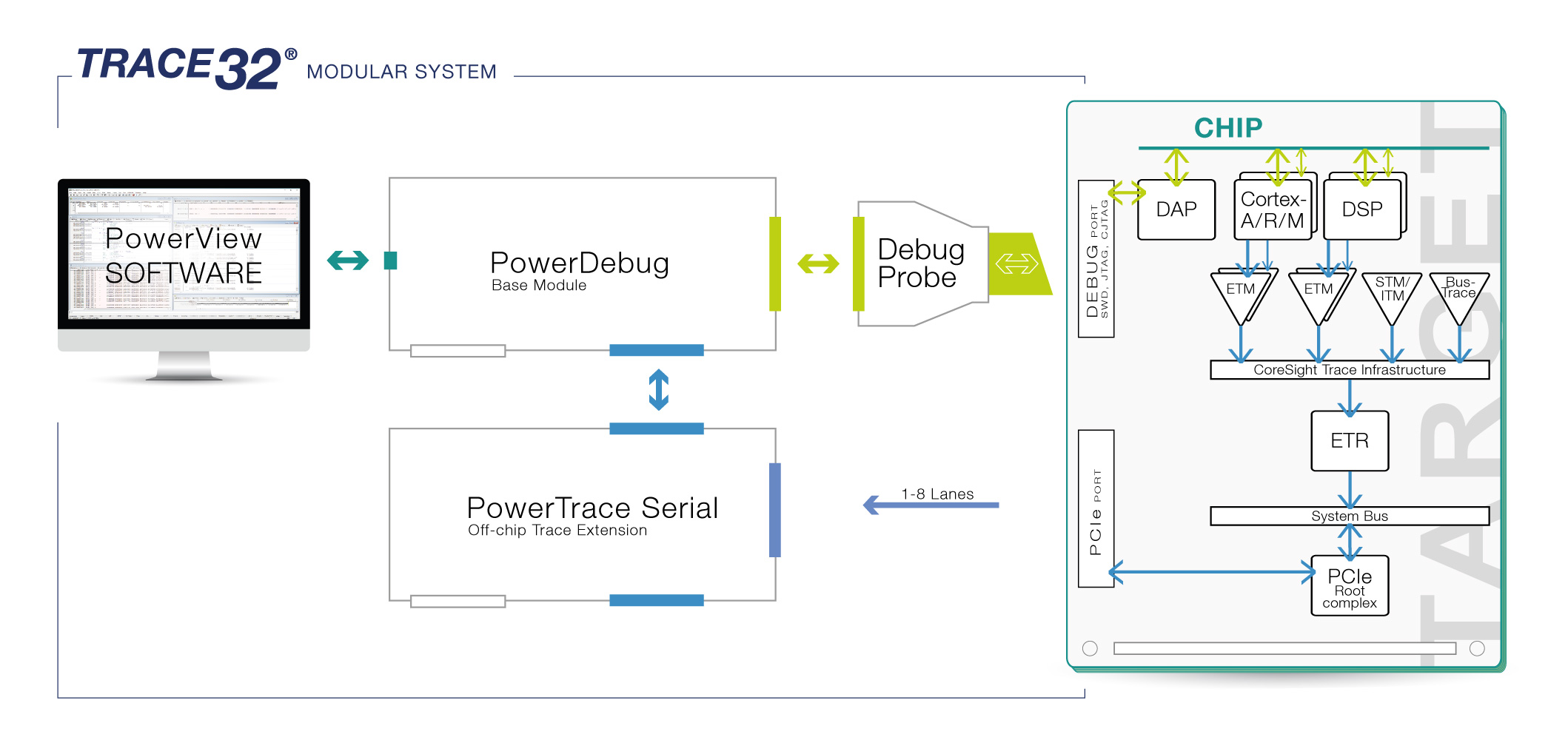

複数のコアやその他のシステムソースのプログラムフロー、データアクセス、タスクスイッチを同時に精細にキャプチャします。最大100 GBit/sの高速ビットレートと大容量データバッファにより、PowerTrace Serial 、トップレベルのモジュール相互作用から個々の命令のタイミングまで、デバイスの動作を調べることができます。

デバッグシステムの詳細どのARM コアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

強力なトレースツール

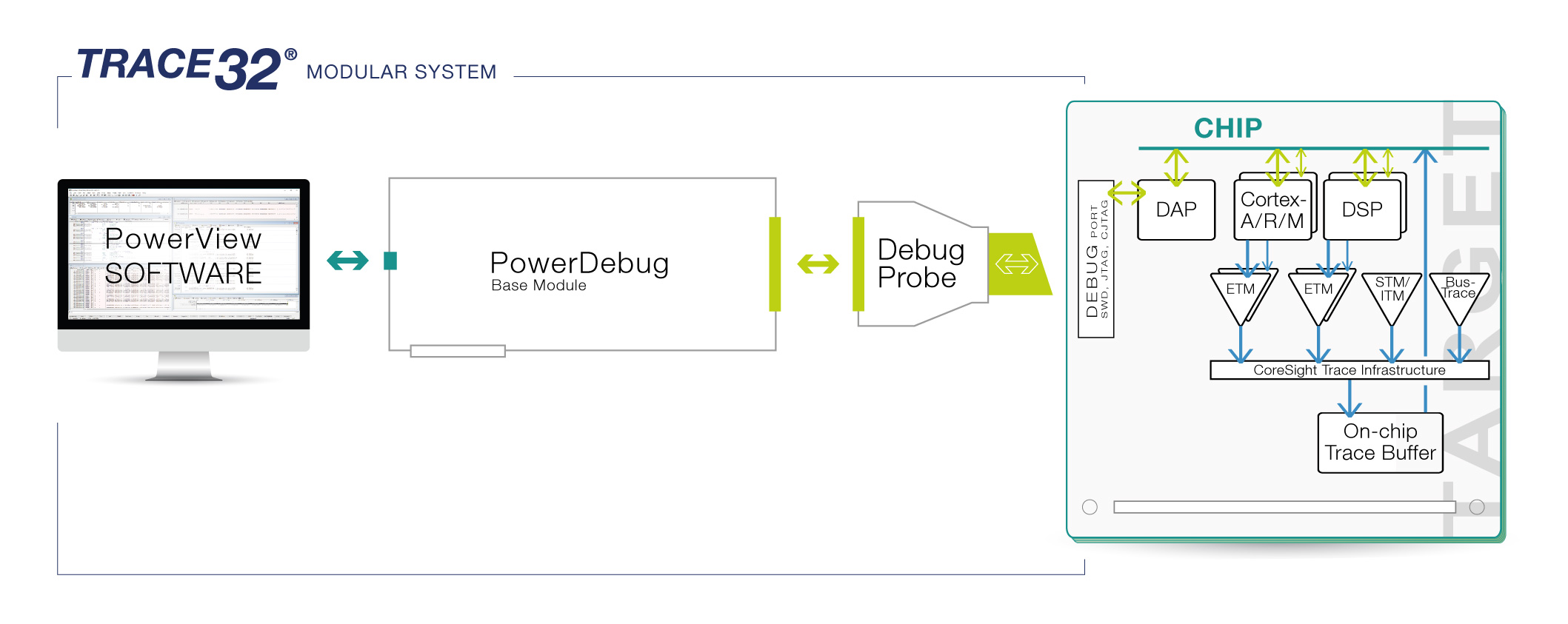

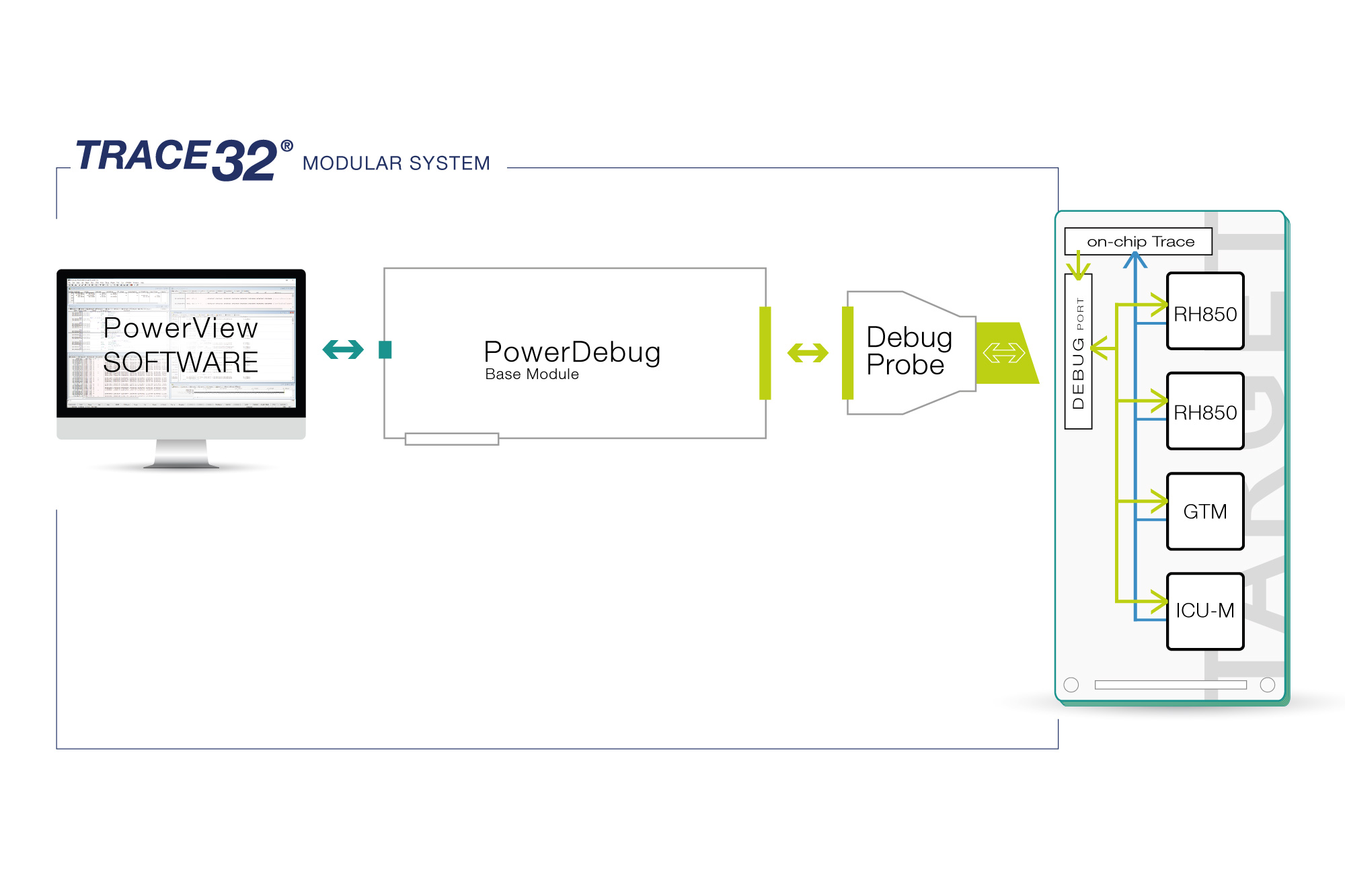

多くのArm®プロセッサは、何らかのトレースインターフェースを備えており、プログラムフローとオプションのデータトレースを実行時に非侵入的に生成し、専用のオンチップ・メモリに保存するか、トレースポート(通常はTPIUまたはHSSTP)を介してオフチップにスプールすることができます。インスツルメンテッドトレースのオプションもあり、デバッグワークフローを強化するために、重要なイベントだけをログに記録することができます。SoCに関連する多くのコアは、トレースデータを生成し、トレースストリームに挿入することができ、効果的にすべてのコアが物理的なトレース接続を共有することができます。このトレース情報は、タイムスタンプされ、ターゲットシステムのあらゆる側面の解析のための信じられないほどの詳細レベルを提供します。

Arm Cortex -M コア用 µTrace® オールインワンソリューション

Arm Cortex-M ベースの組込み設計に対応した完全なデバッグトレースシステムのパワーを活用できます。

どのARM コアを使いますか?

当社の定義済みソリューションのカタログをご覧いただき、お客様のプロジェクトに最適なツールセットを見つけてください。

仮想ターゲットのデバッグ

アプリケーションコードとアルゴリズムは、さまざまなArm®ベースの仮想ターゲットを使用してテストし、改良することができます。TRACE32 、実世界のハードウェアと同じ使い慣れたツールセットとユーザーインターフェイスを使用して、仮想ターゲットで作業することができます。これにより、余分なトレーニングの必要性が減り、すぐにスピードアップして初日から生産性を上げることができます。

デバッグとトレースの両方でマルチコアデバッグAPI(MCD)またはデバッグのためのGDBをサポートしている任意の仮想ターゲットで動作します。Armの高速モデルと IRIS インタフェースをフルサポートします。

ARM対応サードパーティツール

以下の機能は、TRACE32 がサポートするすべてのアーキテクチャで利用可能です。お使いのデバイスやツールがここに掲載されていない場合は、お問い合わせください。